# TM-1300 Data Book

|    | Foreword                         | 13 | System Boot                          |

|----|----------------------------------|----|--------------------------------------|

|    | Table of Contents                | 14 | Image Coprocessor                    |

| 1  | Pin List                         | 15 | Variable Length Decoder              |

| 2  | Overview                         | 16 | I <sup>2</sup> C Interface           |

| 3  | DSPCPU Architecture              | 17 | Synchronous Serial Interface         |

| 4  | Custom Operations for Multimedia | 18 | JTAG Functional Specification        |

| 5  | Cache Architecture               | 19 | On-Chip Semaphore Assist Device      |

| 6  | Video In                         | 20 | Arbiter                              |

| 7  | Enhanced Video Out               | 21 | Power Management                     |

| 8  | Audio In                         | 22 | PCI-XIO Bus Functional Specification |

| 9  | Audio Out                        | Α  | DSPCPU Operations                    |

| 10 | SPDIF Out                        | В  | MMIO Register Summary                |

| 11 | PCI Interface                    | С  | Endian-ness                          |

| 12 | SDRAM Memory System              |    | Index                                |

|    |                                  |    |                                      |

© 1999 Philips Electronics North America Corporation All rights reserved.

See Terms and Conditions on the next page.

May 2000

PRODUCT SPECIFICATION

#### TERMS AND CONDITIONS

Philips Semiconductors and Philips Electronics North America Corporation reserve the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or most work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or most work right infringement, unless otherwise specified. Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### LIFE SUPPORT APPLICATIONS

Philips Semiconductors and Philips Electronics North America Corporation products are not designed for use in life support appliances, devices, or systems where malfunction of a Philips Semiconductors and Philips Electronics North America Corporation product can reasonably be expected to result in a personal injury. Philips Semiconductors and Philips Electronics North America Corporation customers using or selling Philips Semiconductors and Philips Electronics North America Corporation products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors and Philips Electronics North America Corporation for any damages resulting from improper use or sale.

Philips Semiconductors and Philips Electronics North America Corporation register eligible circuits under the Semiconductor Chips Protection Act.

#### **DEFINITIONS**

| Data Sheet<br>Identification | Product Status           | Definition                                                                                                                                                                                                                                                 |

|------------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Objective<br>Specification   | Formative or in Design   | This data sheet contains the design target or goal specifications for product development. Specifications may change in any manner without notice.                                                                                                         |

| Preliminary<br>Specification | Preproduction<br>Product | This data sheet contains preliminary data, and supplementary data will be published at a later date. Philips Semiconductors reserves the right to make changes at any time without notice in order to improve design and supply the best possible product. |

| Product<br>Specification     | Full<br>Production       | This data sheet contains Final Specifications. Philips Semiconductors reserves the right to make changes at any time without notice, in order to improve the design and supply the best possible product.                                                  |

© 1999 Philips Electronics North America Corporation, 1999

All rights reserved.

Printed in U.S.A.

## **Foreword**

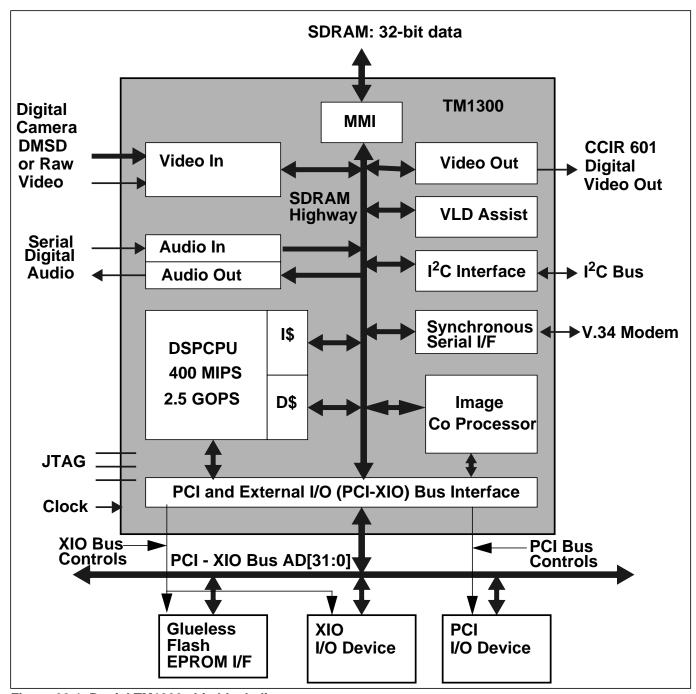

The TriMedia™ TM-1300 is a higher speed, functionally enhanced version of the TM-1000 media processor.

TM-1300 contains an ultra-high performance Very Long Instruction Word processor, as well as a complete intelligent video and audio input/output subsystem. The processor has an instruction set that is optimized for processing audio, video and graphics. It includes powerful SIMD multimedia operators for eight- and 16-bit signal datatypes as well as a full complement of 32-bit IEEE compatible floating point operations.

TM-1300 is intended as a multi-standard programmable video, audio and graphics processor. It can either be used standalone, or as an accelerator to a general purpose processor.

The architecture of the TriMedia family came about as the result of many years of effort of many dedicated individuals. Going back in history, the origin of TriMedia was laid by the LIFE-1 VLIW processor, designed by Junien Labrousse and myself in 1987. Work continued afterwards in Philips Research Labs, Palo Alto. My special thanks go to the entire Palo Alto research team: Mike Ang, Uzi Bar-Gadda, Peter Donovan, Martin Freeman, Eino Jacobs, Beomsup Kim, Bob Law, Yen Lee, Vijay Mehra, Pieter van der Meulen, Ross Morley, Mariette Parekh, Bill Sommer, Artur Sorkin and Pierre Uszynski.

The Palo Alto period matured the architecture—we ported all video and audio algorithms that we could find to the compiler/simulator and refined the operation set. In addition, we learned how to give the architecture a market direction. In May 1994, Philips management—in particular Cees-Jan Koomen, Eddy Odijk, Theo Claasen and Doug Dunn—decided to develop TriMedia into a major Philips Semiconductors product line.

Under the guidance of Keith Flagler, the TriMedia team was built. All of them contributed to take this from a set of interesting ideas to a reliable and competitive product in a short period of time. The initial TriMedia team included Fuad Abu Nofal, Karel Allen, Mike Ang, Robert Aquino, Manju Asthana, Patrick de Bakker, Shiv Balakrishnan, Jai Bannur, Marc Berger, Sunil Bhandari, Rusty Biesele, Ahmet Bindal, David Blakely, Hans Bouwmeester, Steve Bowden, Robert Bradfield, Nancy Breede, Shawn Brown, Sujay Chari, Catherine Chen,

Howen Chen, Yan-ming Chen, Yong Cho, Scott Clapper, Matthew Clayson, Paul Coelho, Richard Dodds, Marc Duranton, Darcia Eding, Aaron Emigh, Li Chi Feng, Keith Flagler, Jean Gobert, Sergio Golombek, Mike Grimwood, Yudi Halim, Hari Hampapuram, Carl Hartshorn, Judy Heider, Laura Hrenko, Jim Hsu, Eino Jacobs, Marcel Janssens, Patricia Jones, Hann-Hwan Ju, Jayne Keith, Bhushan Kerur, Ayub Khan, Keith Knowles, Mike Kong, Ashok Krishnamurti, Yen Lee, Patrick Leong, Bill Lin, Laura Ling, Chialun Lu, Naeem Maan, Nahid Mansipur, Mike Maynard, Vijay Mehra, Jun Mejia, Derek Meyer, Prabir Mohanty, Saed Muhssin, Chris Nelson, Stephen Ness, Keith Ngo, Francis Nguyen, Kathleen Nguyen, Derek Noonburg, Ciaran O'Donnel, Sang-Ju Park, Charles Peplinski, Gene Pinkston, Maryam Pirayou, Pardha Potana, Bill Price, Victor Ramamoorthy, Babu Rao Kandamilla, Ehsan Rashid, Selliah Rathnam, Margaret Redmond, Donna Richardson, Alan Rodgers, Tilakray Roychoudhury, Hani Salloum, Chris Salzmann, Bob Seltzer, Ravi Selvaraj, Jim Shimandle, Deepak Singh, Bill Sommer, Juul van der Spek, Manoj Srivastava, Renga Sundararajan, Ken-Sue Tan, Ray Ton, Steve Tran, Cynthia Tripp, Ching-Yih Tseng, Allan Tzeng, Barbara Vendelin, John Vivit, Rudy Wang, Rogier Wester, Wayne Wonchoba, Anthony Wong, Sara Wu, David Wyland, Ken Xie, Vincent Xie, Bettina Yeung, Robert Yin, Charles Young, Grace Yun, Elena Zelayeta and Vivian Zhu.

Expert help and feedback was received from many. In particular, I'd like to mention Kees van Zon of Philips Eindhoven for the help with filtering-related issues, and Craig Clapp of PictureTel for excellent feedback on all aspects of the architecture.

My special thanks go to Joe Kostelec. He made me understand that my ambitions could better be realized in California than in Europe. Furthermore, his vision and his wisdom are credited with keeping this project alive and growing until the 'investment decision.'

The vision of a universal media accelerator is credited to Jaap de Hoog. Jaap, I wish you were here to see it come to fruition.

-Gerrit Slavenburg

## **Table of Contents**

## **Foreword**

| 1 | Pin List                                                                   |

|---|----------------------------------------------------------------------------|

|   | 1.1 TM1300 versus TM1100                                                   |

|   | 1.2 Boundary Scan Notice                                                   |

|   | 1.3 I/O Circuit Summary                                                    |

|   | 1.4 Signal Pin List                                                        |

|   | 1.5 Power Pin List                                                         |

|   | 1.6 Pin Reference Voltage                                                  |

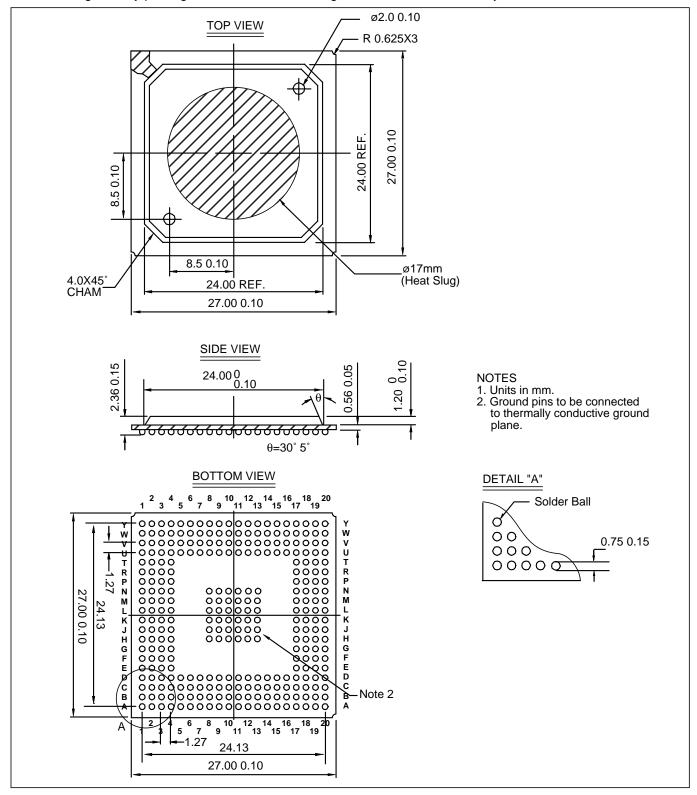

|   | 1.7 Package                                                                |

|   | 1.8 Ordering Information                                                   |

|   | 1.9 Parametric Characteristics                                             |

|   | 1.9.1 Operating Range and Thermal Characteristics                          |

|   | 1.9.2 Absolute Maximum Ratings1-11                                         |

|   | 1.9.3 Power Supply Sequencing1-11                                          |

|   | 1.9.4 DC/AC Characteristics                                                |

|   | 1.9.4.1 TM-1300 and DSPCPU Core Current and Power Consumption Details 1-12 |

|   | 1.9.4.2 TM-1300 Peripheral Current Consumption Details                     |

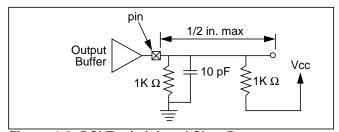

|   | 1.9.4.3 STRG3, STRG5 type I/O circuit                                      |

|   | 1.9.4.4 NORM3 type I/O circuit                                             |

|   | 1.9.4.5 WEAK5 type I/O circuit                                             |

|   | 1.9.4.6 IICOD (I2c) type I/O circuit                                       |

|   | 1.9.4.7 SDRAM interface timing                                             |

|   | 1.9.4.8 PCI Bus timing                                                     |

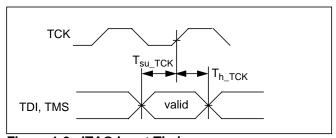

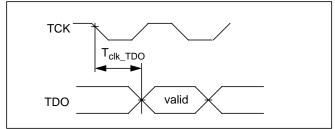

|   | 1.9.4.9 JTAG I/O timing                                                    |

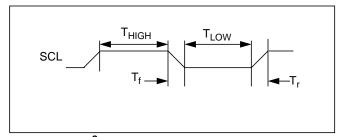

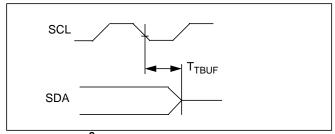

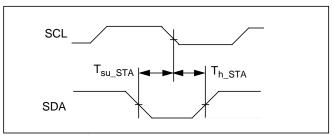

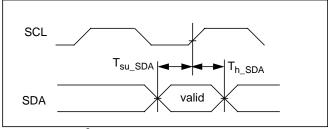

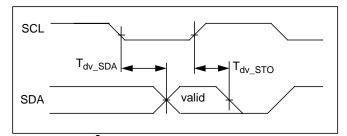

|   | 1.9.4.10 I2C I/O timing                                                    |

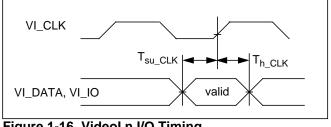

|   | 1.9.4.11 Video In I/O Timing                                               |

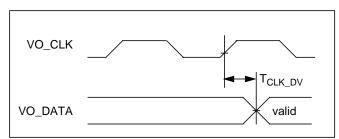

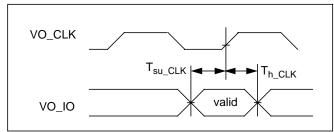

|   | 1.9.4.12 Video Out I/O Timing                                              |

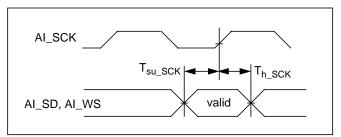

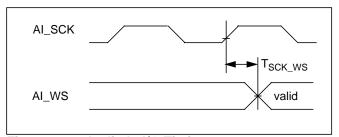

|   | 1.9.4.13 AudioIn I/O timing                                                |

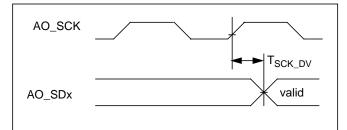

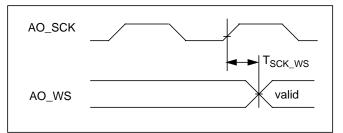

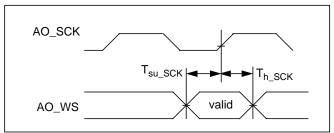

|   | 1.9.4.14 Audio Out I/O timing                                              |

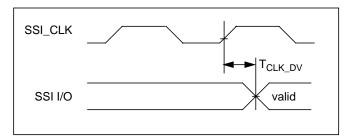

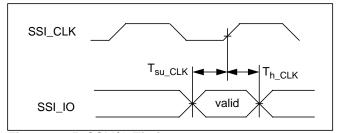

|   | 1.9.4.15 SSI I/O timing                                                    |

| 2 | Overview                                                                   |

|   | 2.1 Introduction                                                           |

|   | 2.2 TM1300 Fundamentals                                                    |

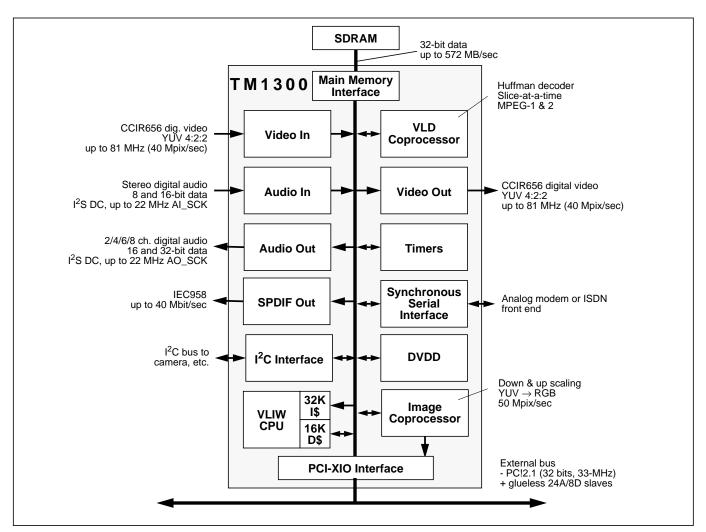

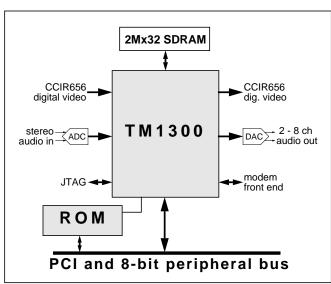

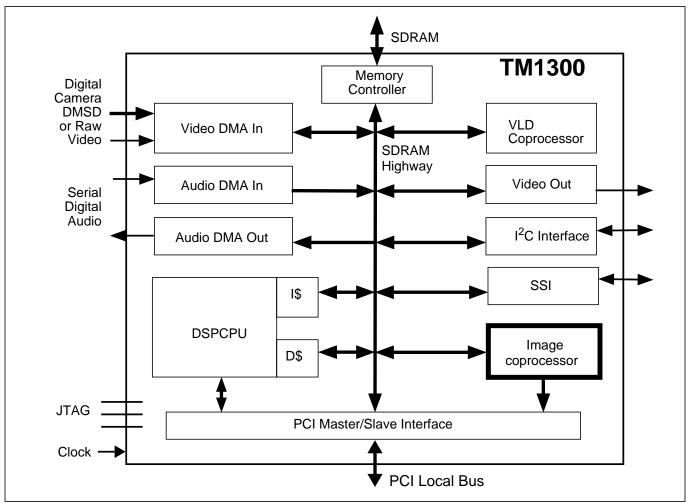

2.3 TM1300 Chip Overview

2-2

2.4 Brief Examples of Operation

2-3

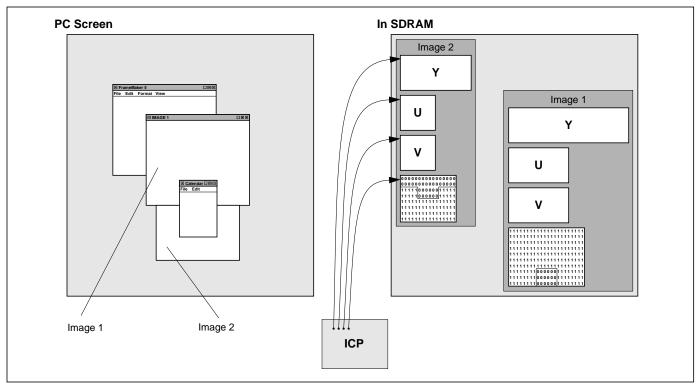

| 2.4.1 Video Decompression in a PC                        |

|----------------------------------------------------------|

| 2.4.2 Video Compression                                  |

| 2.5 Introduction to TM1300 Blocks                        |

| 2.5.1 Internal 'Data Highway' Bus2-3                     |

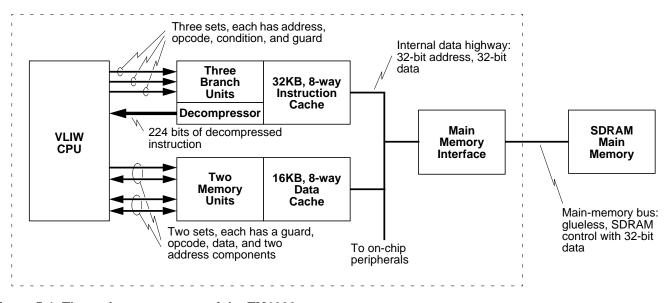

| 2.5.2 VLIW Processor Core                                |

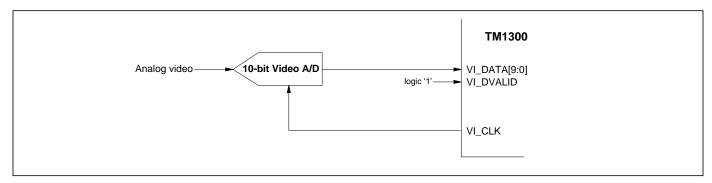

| 2.5.3 Video In Unit                                      |

| 2.5.4 Enhanced Video Out Unit                            |

| 2.5.5 Image Coprocessor                                  |

| 2.5.6 Variable-Length Decoder (VLD)                      |

| 2.5.7 Audio In and Audio Out Units                       |

| 2.5.8 S/PDIF Out Unit                                    |

| 2.5.9 Synchronous Serial Interface                       |

| 2.5.10 I2C Interface                                     |

| 2.6 New In TM1300 (Versus TM1100)                        |

| 2.7 New In TM1300 (Versus TM1000)                        |

|                                                          |

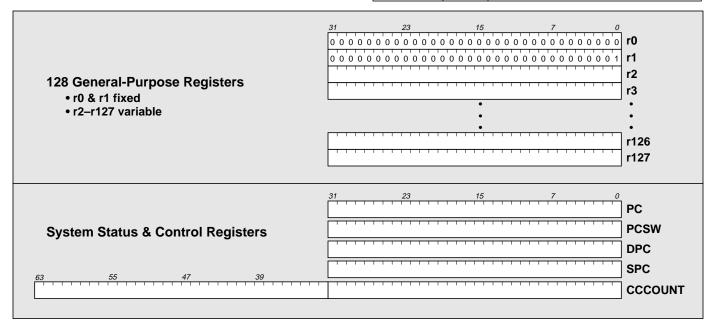

| DSPCPU Architecture                                      |

| 3.1 Basic Architecture Concepts                          |

| 3.1.1 New in TM1300                                      |

| 3.1.2 Register Model                                     |

| 3.1.3 Basic DSPCPU Execution Model                       |

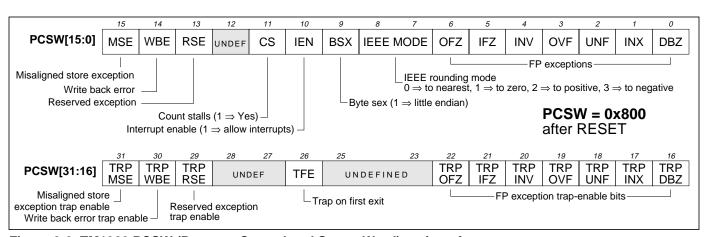

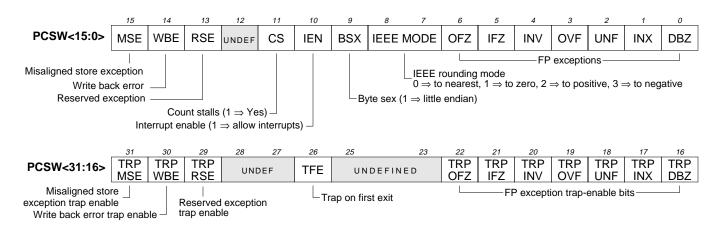

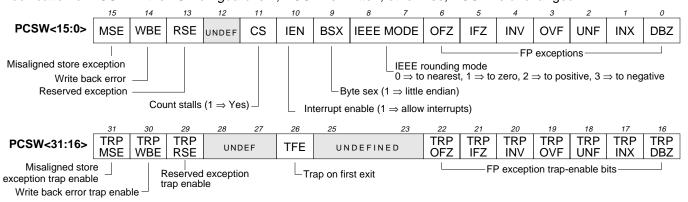

| 3.1.4 PCSW Overview                                      |

| 3.1.5 SPC and DPC—Source and Destination Program Counter |

| 3.1.6 CCCOUNT—Clock Cycle Counter                        |

| 3.1.7 Boolean Representation                             |

| 3.1.8 Integer Representation                             |

| 3.1.9 Floating Point Representation                      |

| 3.1.10 Addressing Modes                                  |

| 3.1.11 Software Compatibility                            |

| 3.2 Instruction Set Overview                             |

| 3.2.1 Guarding (Conditional Execution)                   |

| 3.2.2 Load and Store Operations                          |

| 3.2.3 Compute Operations                                 |

| 3.2.4 Special-Register Operations                        |

| 3.2.5 Control-Flow Operations                            |

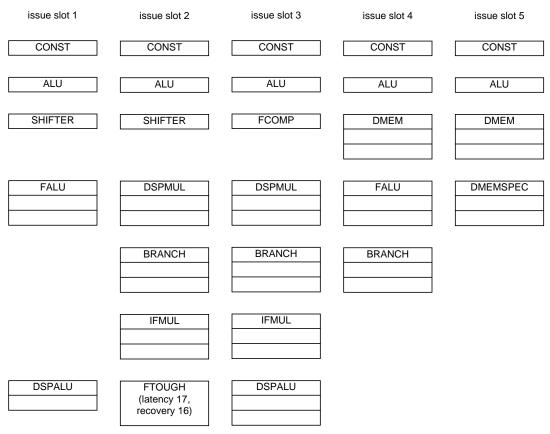

| 3.3 TM1300 Instruction Issue Rules                       |

| 3.4 Memory and MMIO                                      |

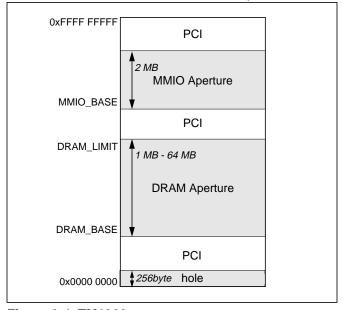

| 3.4.1 Memory Map                                         |

| 3.4.2 The Memory Hole                                    |

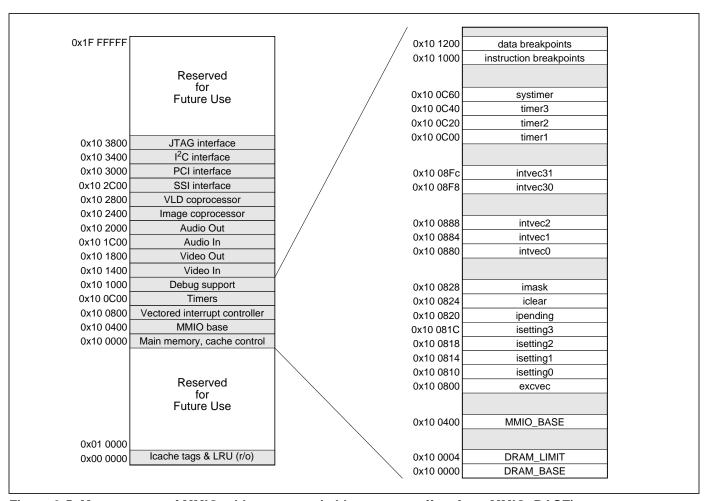

| 3.4.3 MMIO Memory Map                                    |

| 3.5 Special Event Handling                               |

|                                                          |

|   | 3.5.1 RESET                                              | 3-9  |

|---|----------------------------------------------------------|------|

|   | 3.5.2 EXC (Exceptions)                                   | 3-9  |

|   | 3.5.3 INT and NMI (Maskable and Non-Maskable Interrupts) | 3-9  |

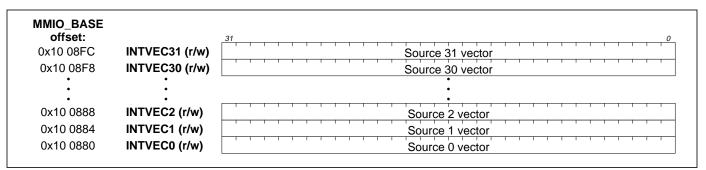

|   | 3.5.3.1 Interrupt vectors                                | 3-9  |

|   | 3.5.3.2 Interrupt modes                                  | 3-10 |

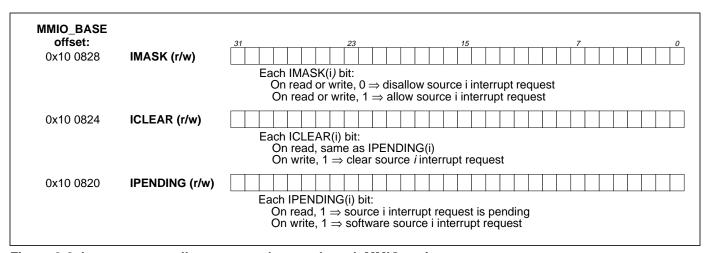

|   | 3.5.3.3 Device interrupt acknowledge                     | 3-10 |

|   | 3.5.3.4 Interrupt priorities                             | 3-10 |

|   | 3.5.3.5 Interrupt masking                                | 3-10 |

|   | 3.5.3.6 Software interrupts and acknowledgment           | 3-11 |

|   | 3.5.3.7 NMI sequentialization                            | 3-11 |

|   | 3.5.3.8 Interrupt source assignment                      | 3-11 |

|   | 3.6 TM1300 to Host Interrupts                            | 3-11 |

|   | 3.7 Host to TM1300 Interrupts                            | 3-12 |

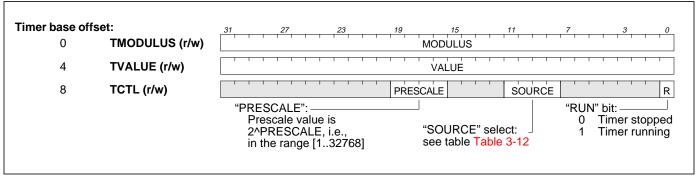

|   | 3.8 Timers                                               | 3-12 |

|   | 3.9 Debug Support                                        | 3-13 |

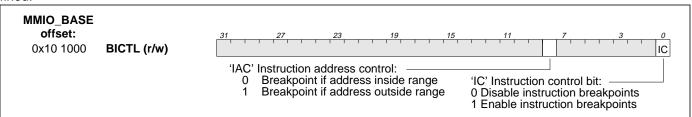

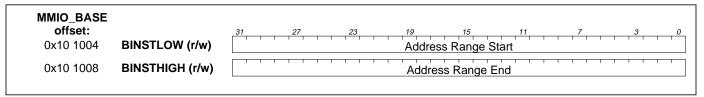

|   | 3.9.1 Instruction Breakpoints                            | 3-13 |

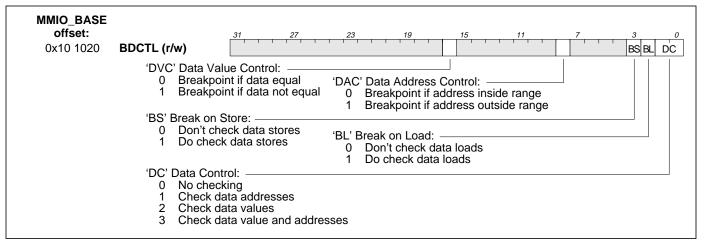

|   | 3.9.2 Data Breakpoints                                   | 3-14 |

| 4 | Custom Operations for Multimodia                         |      |

| 4 | Custom Operations for Multimedia                         |      |

|   | 4.1 Custom OperationS Overview                           |      |

|   | 4.1.1 Custom Operation Motivation                        |      |

|   | 4.1.2 Introduction to Custom Operations                  |      |

|   | 4.1.3 Example Uses of Custom Ops                         |      |

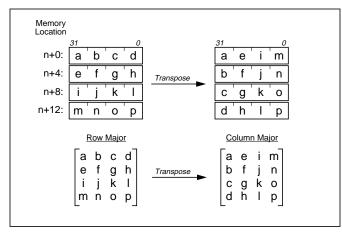

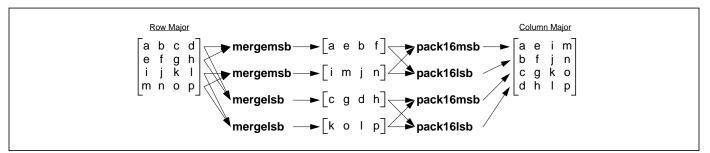

|   | 4.2 Example 1: Byte-Matrix Transposition                 |      |

|   | 4.3 Example 2: MPEG Image Reconstruction                 |      |

|   | 4.4 Example 3: Motion-Estimation Kernel                  |      |

|   | 4.4.1 A Simple Transformation                            |      |

|   | 4.4.2 More Unrolling                                     | 4-10 |

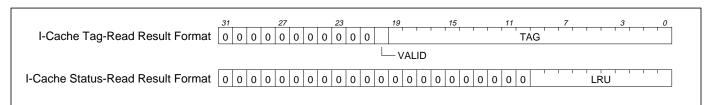

| 5 | Cache Architecture                                       |      |

|   | 5.1 Memory System Overview                               | 5-1  |

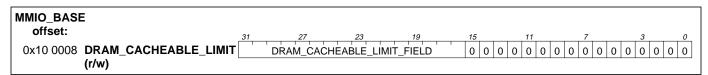

|   | 5.2 DRAM Aperture                                        | 5-2  |

|   | 5.3 Data Cache                                           | 5-3  |

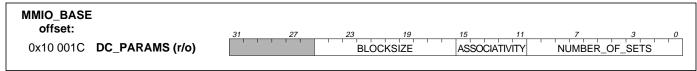

|   | 5.3.1 General Cache Parameters                           | 5-3  |

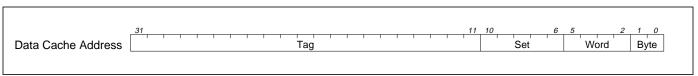

|   | 5.3.2 Address Mapping                                    | 5-3  |

|   | 5.3.3 Miss Processing Order                              |      |

|   | 5.3.4 Replacement Policies, Coherency                    |      |

|   | 5.3.5 Alignment, Partial-Word Transfers, Endian-ness     |      |

|   | 5.3.6 Dual Ports                                         |      |

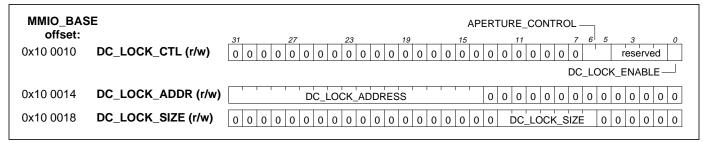

|   | 5.3.7 Cache Locking                                      |      |

|   | 5.3.8 Memory Hole and PCI Aperture Disable               |      |

|   | ·                                                        |      |

6

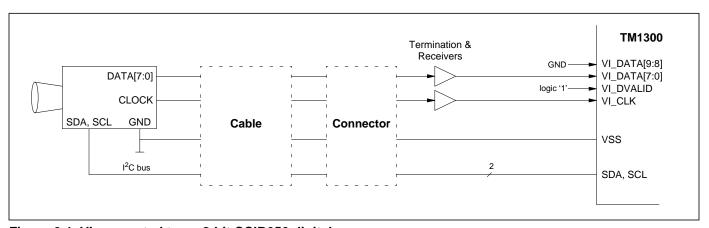

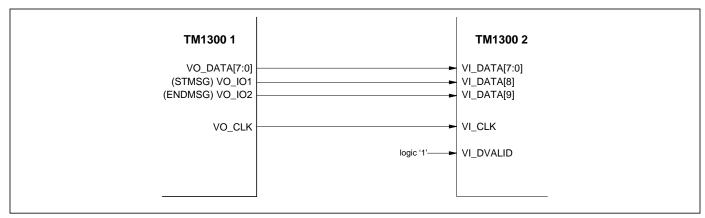

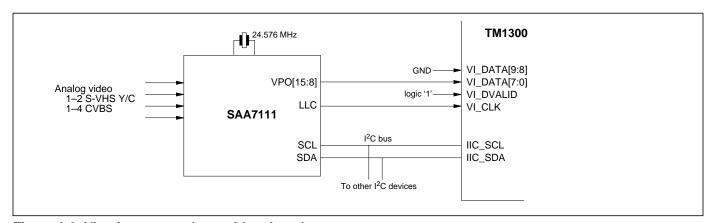

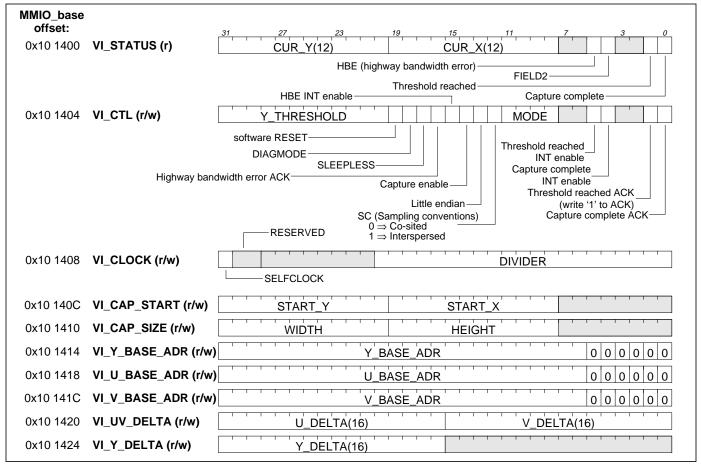

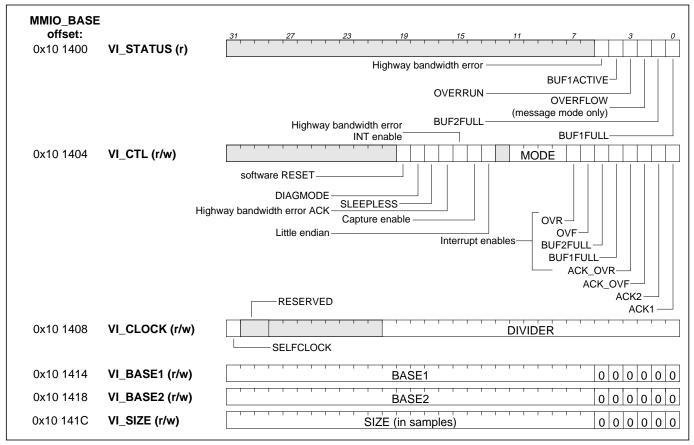

|   | 6.1.3 Power Down and Sleepless                                 | 6-2    |

|---|----------------------------------------------------------------|--------|

|   | 6.1.4 Hardware and Software Reset                              | 6-2    |

|   | 6.2 Clock Generator                                            | 6-3    |

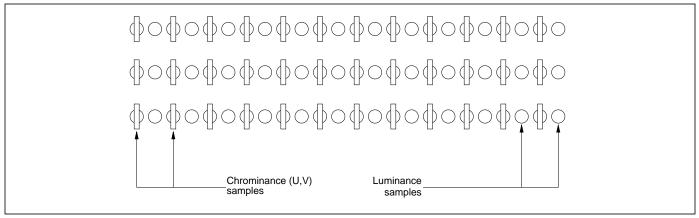

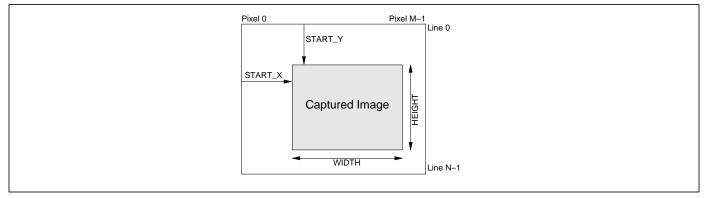

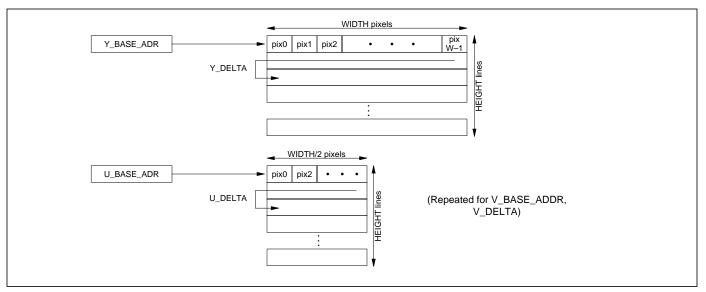

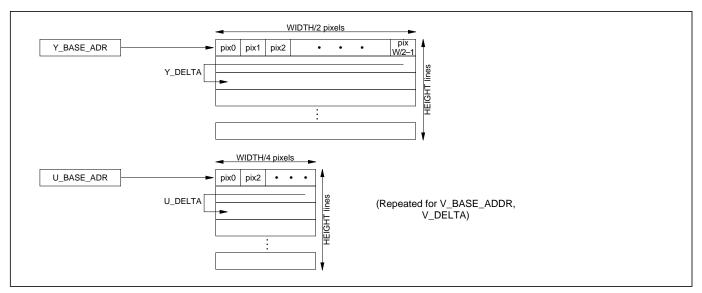

|   | 6.3 Fullres Capture Mode                                       | 6-4    |

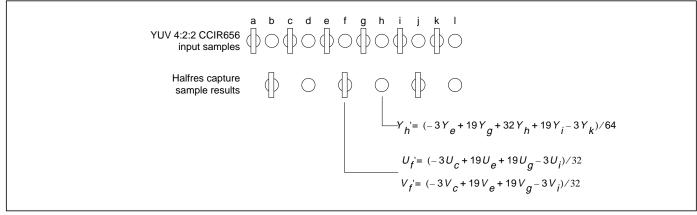

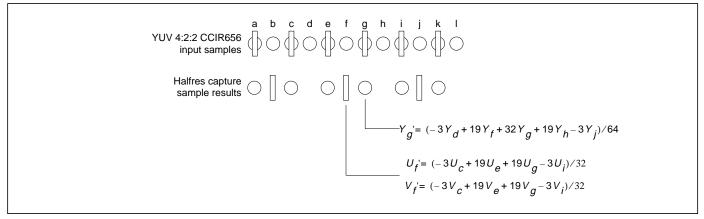

|   | 6.4 Halfres Capture Mode                                       | 6-9    |

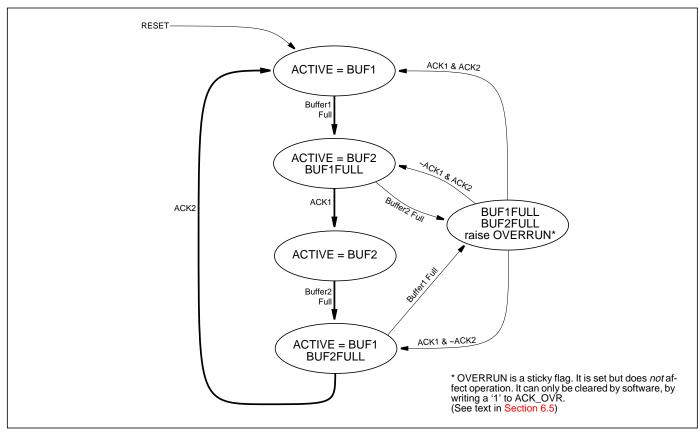

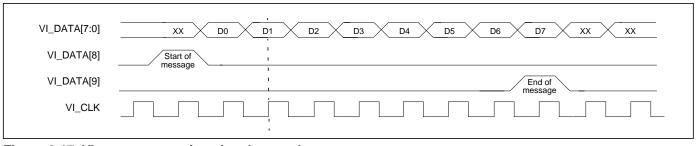

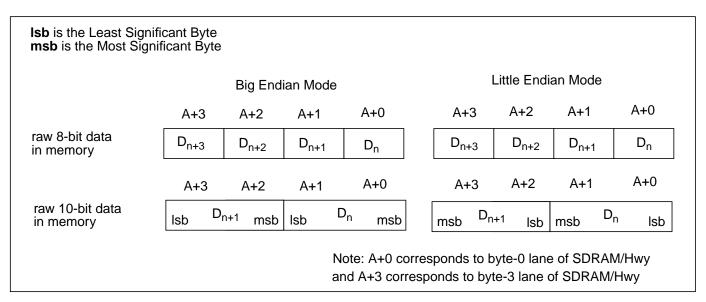

|   | 6.5 Raw Capture Modes                                          | 6-9    |

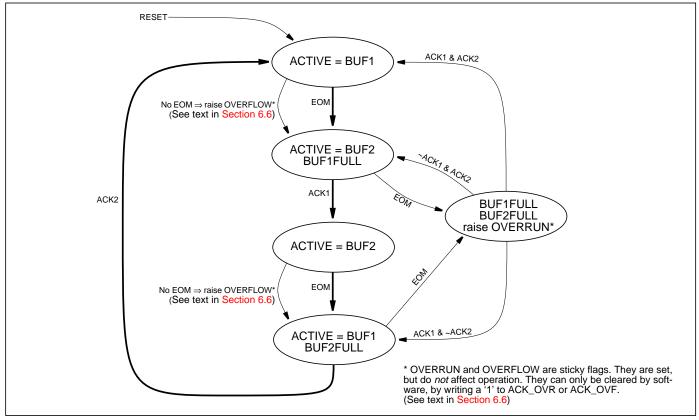

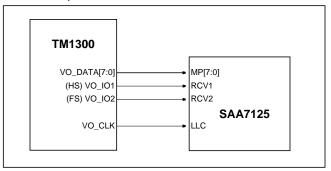

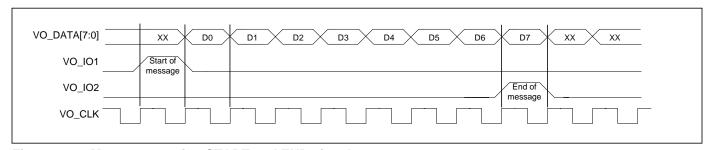

|   | 6.6 Message-Passing Mode                                       | 6-11   |

|   | 6.7 Highway Latency and HBE                                    | 6-12   |

| 7 | Enhanced Video Out                                             |        |

|   | 7.1 Enhanced Video Out Summary                                 | 7-1    |

|   | 7.2 About This Document                                        | . 7-1  |

|   | 7.3 Backward Compatibility                                     | . 7-1  |

|   | 7.4 Function summary                                           | . 7-1  |

|   | 7.4.1 Detailed Feature Descriptions                            | 7-2    |

|   | 7.4.2 Summary of Operation                                     | 7-2    |

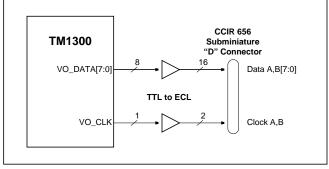

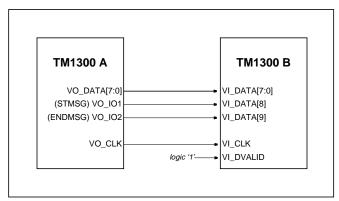

|   | 7.5 Interface                                                  | 7-2    |

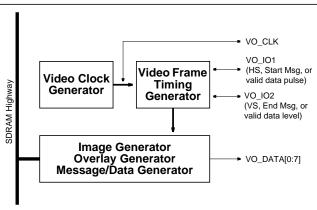

|   | 7.6 Block Diagram                                              | 7-3    |

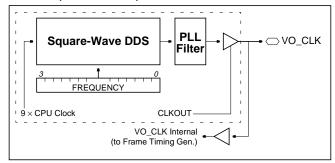

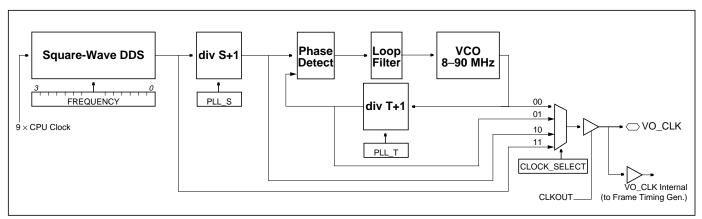

|   | 7.7 Clock System                                               | 7-3    |

|   | 7.8 Image Timing                                               | 7-4    |

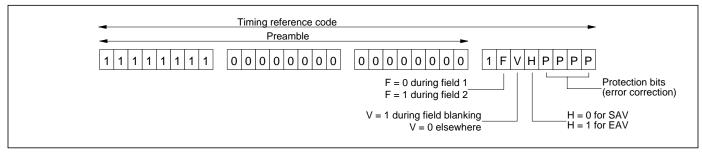

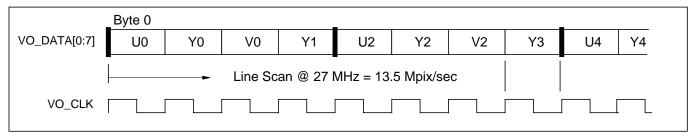

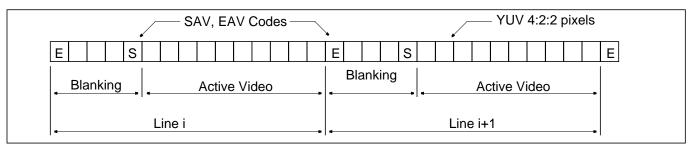

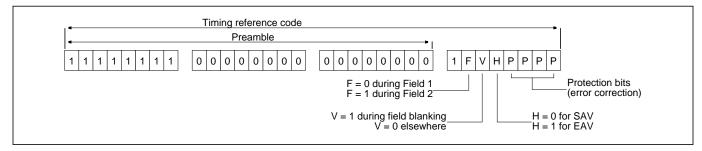

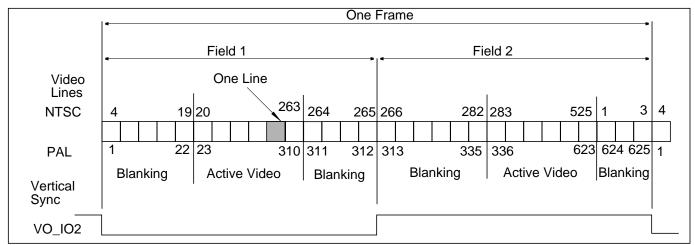

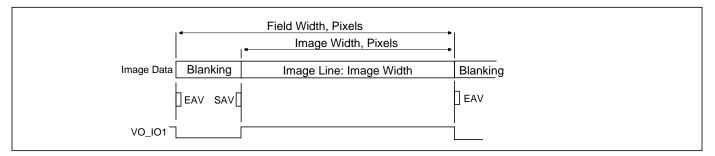

|   | 7.8.1 CCIR 656 Pixel Timing                                    | 7-4    |

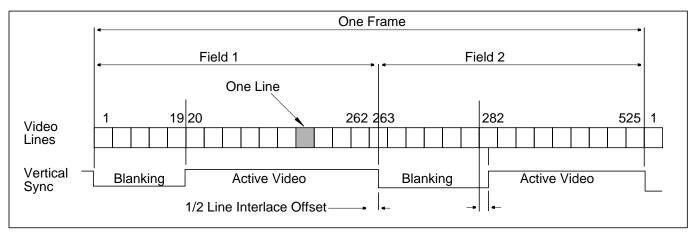

|   | 7.8.2 CCIR 656 Line Timing                                     | 7-4    |

|   | 7.8.3 SAV and EAV Codes                                        | 7-5    |

|   | 7.8.4 Video Clipping                                           | 7-5    |

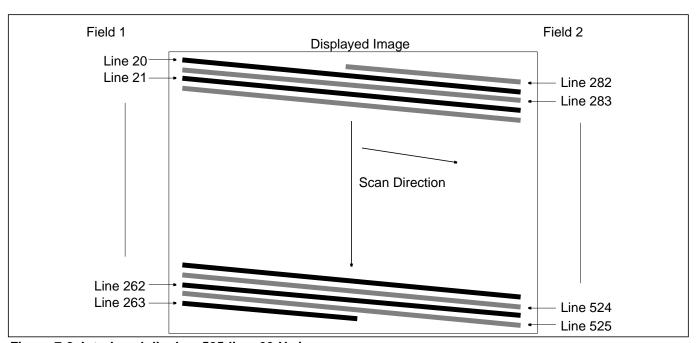

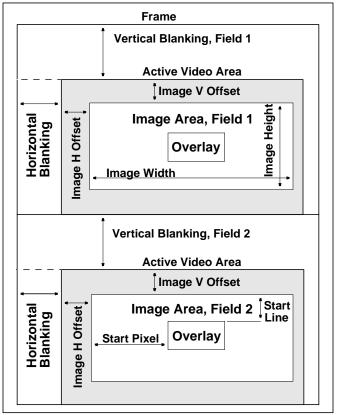

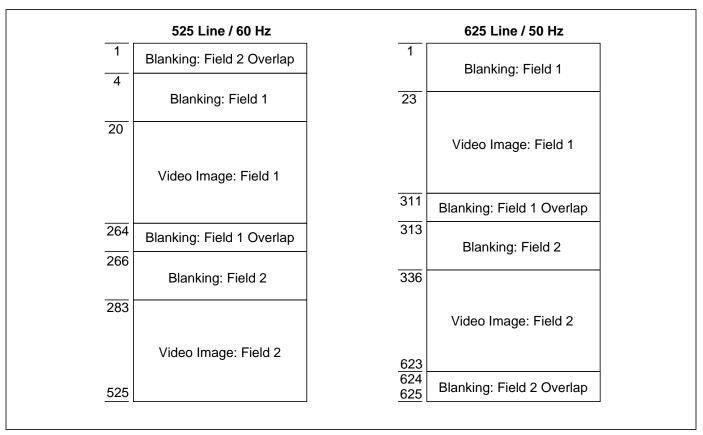

|   | 7.8.5 CCIR 656 Frame Timing                                    | 7-6    |

|   | 7.9 Enhanced Video Out Timing Generation                       | 7-6    |

|   | 7.9.1 Active Video Area                                        | 7-6    |

|   | 7.9.2 SAV and EAV Overlap Period                               | 7-7    |

|   | 7.9.3 Control of Frame and Image Counters                      | . 7-7  |

|   | 7.9.4 Horizontal and Frame Timing Signals                      | . 7-7  |

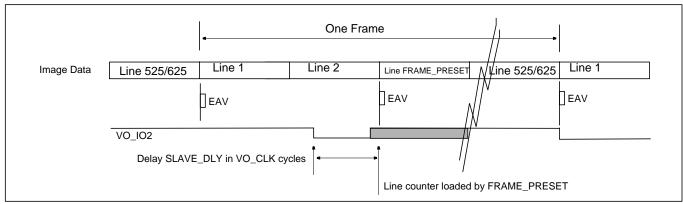

|   | 7.10 Genlock Mode                                              | 7-8    |

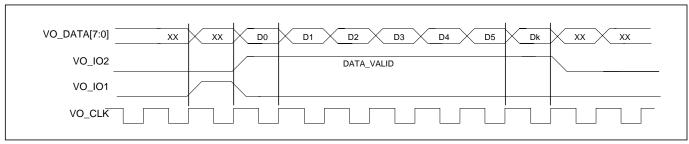

|   | 7.11 Data Transfer Timing                                      |        |

|   | 7.12 Image Data Memory Formats                                 | . 7-9  |

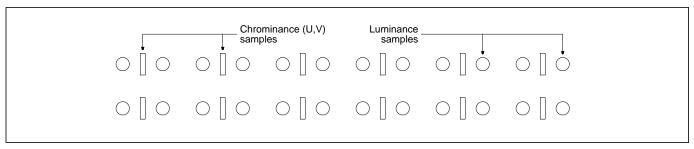

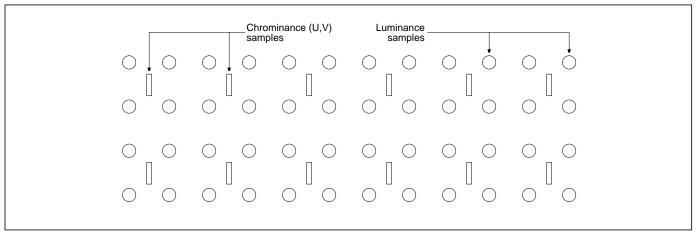

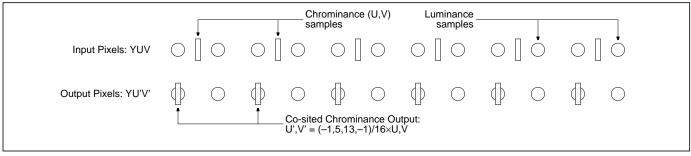

|   | 7.12.1 Video Image Formats                                     | 7-9    |

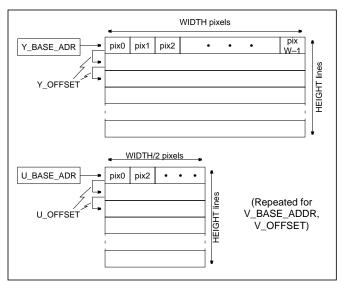

|   | 7.12.2 Planar Storage of Video Image Data in Memory            | . 7-9  |

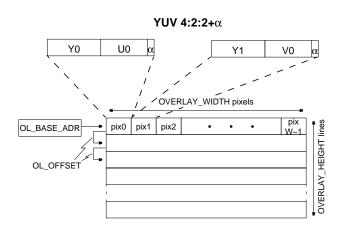

|   | 7.12.3 Graphics Overlay Image Format                           | 7-10   |

|   | 7.13 Video Image Conversion Algorithms                         | 7-11   |

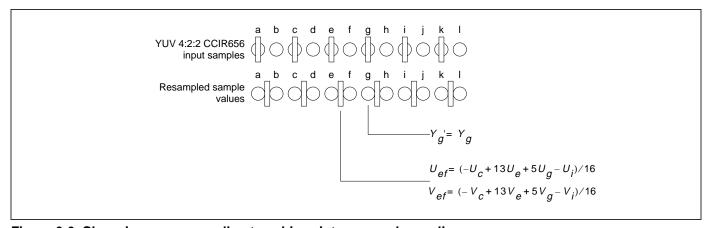

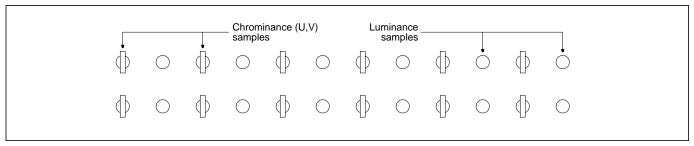

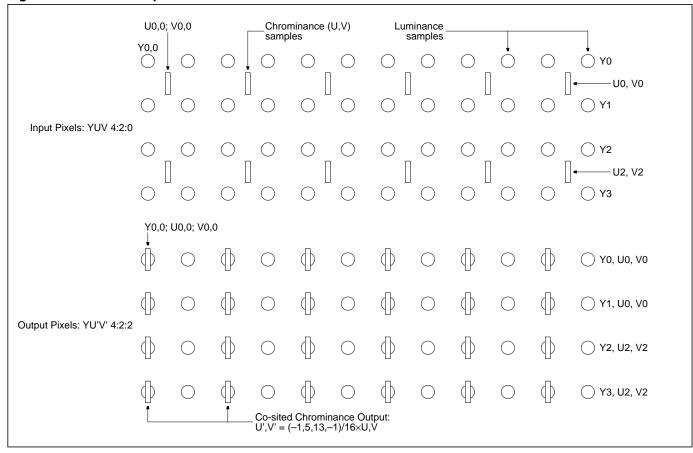

|   | 7.13.1 YUV 4:2:2 Interspersed to YUV 4:2:2 Co-sited Conversion | . 7-11 |

|   | 7.13.2 YUV 4:2:0 to YUV 4:2:2 Co-sited Conversion              | . 7-11 |

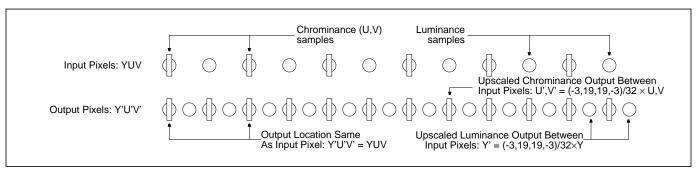

|   | 7.13.3 YUV-2x Upscaling                                        |        |

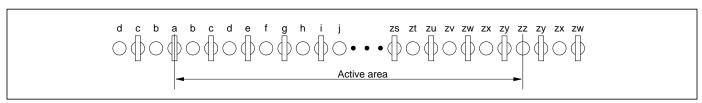

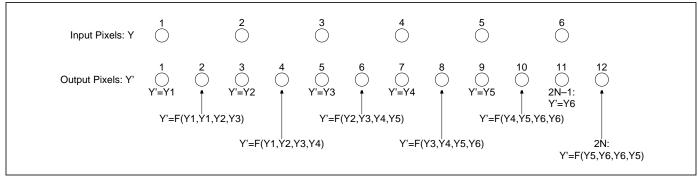

|   | 7.13.4 Pixel Mirroring for Four-tap Filters                    | 7-12   |

|   | 7.14 EVO Operating Modes                            | 7-13 |

|---|-----------------------------------------------------|------|

|   | 7.15 Video Processing                               | 7-13 |

|   | 7.15.1 Alpha Blending                               | 7-13 |

|   | 7.15.2 Chroma Keying                                | 7-14 |

|   | 7.15.3 Programmable Clipping                        | 7-14 |

|   | 7.16 MMIO Registers                                 | 7-14 |

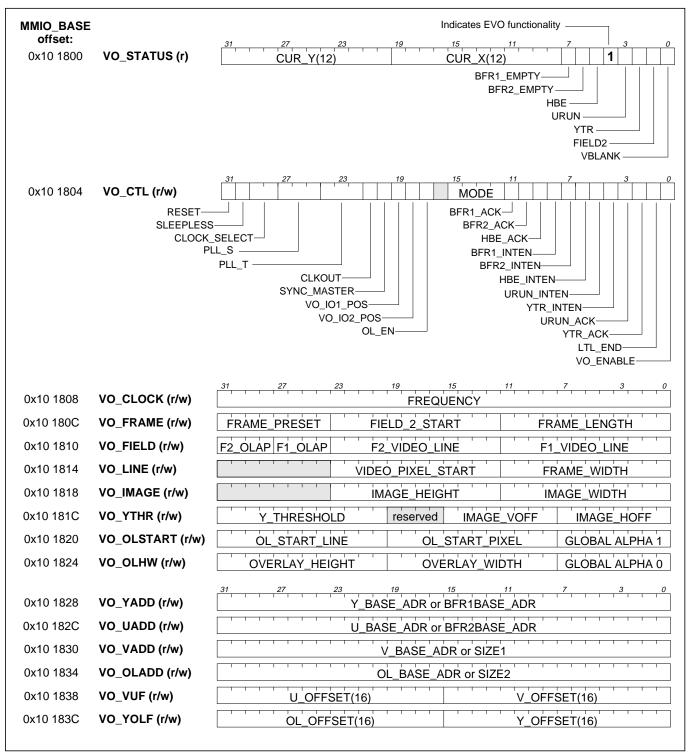

|   | 7.16.1 VO Status Register (VO_STATUS)               | 7-14 |

|   | 7.16.2 VO Control Register (VO_CTL)                 | 7-15 |

|   | 7.16.3 VO-Related Registers                         | 7-15 |

|   | 7.16.3.1 Frame and field timing control             | 7-16 |

|   | 7.16.3.2 Recommended values for timing registers    | 7-16 |

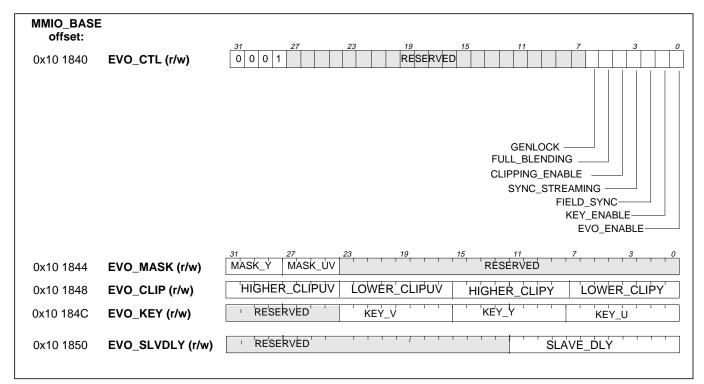

|   | 7.16.4 EVO Control Register (EVO_CTL)               | 7-16 |

|   | 7.16.5 EVO-Related Registers                        | 7-20 |

|   | 7.17 Enhanced Video Out Operation                   | 7-20 |

|   | 7.17.1 Video Refresh Modes                          | 7-22 |

|   | 7.17.2 Data-transfer Modes                          | 7-22 |

|   | 7.17.3 Interrupts and Error Conditions              | 7-23 |

|   | 7.17.4 Latency and Bandwidth Requirements           | 7-23 |

|   | 7.17.5 Power Down and Sleepless                     | 7-24 |

|   | 7.18 DDS and PLL Filter Details                     | 7-24 |

| 8 | Audio In                                            |      |

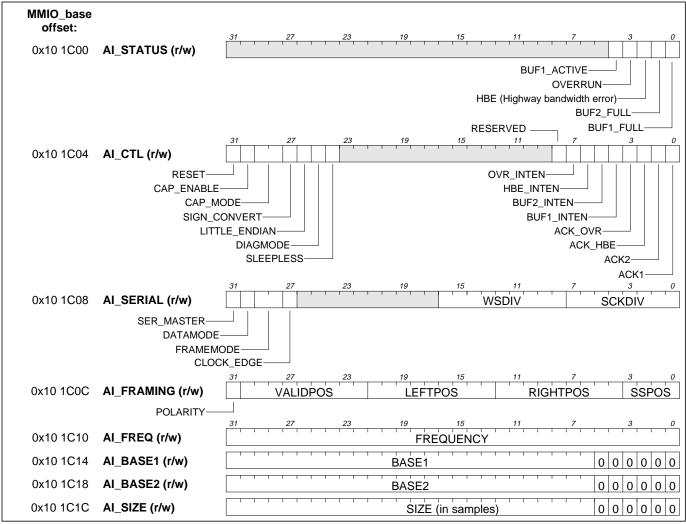

|   | 8.1 Audio In Overview                               | 8-1  |

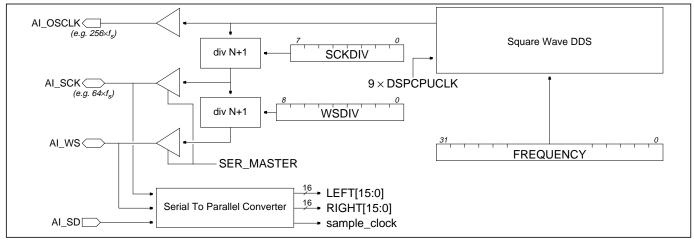

|   | 8.2 External Interface                              |      |

|   | 8.3 Clock System                                    |      |

|   | 8.3.1 TM1300 Improved Mode                          |      |

|   | 8.3.2 TM1000 Compatibility Mode                     |      |

|   | 8.4 Clock System Operation                          |      |

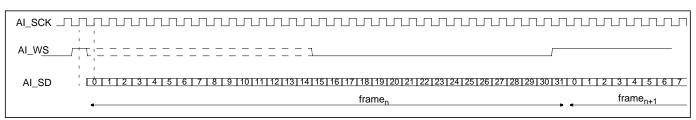

|   | 8.5 Serial Data Framing                             |      |

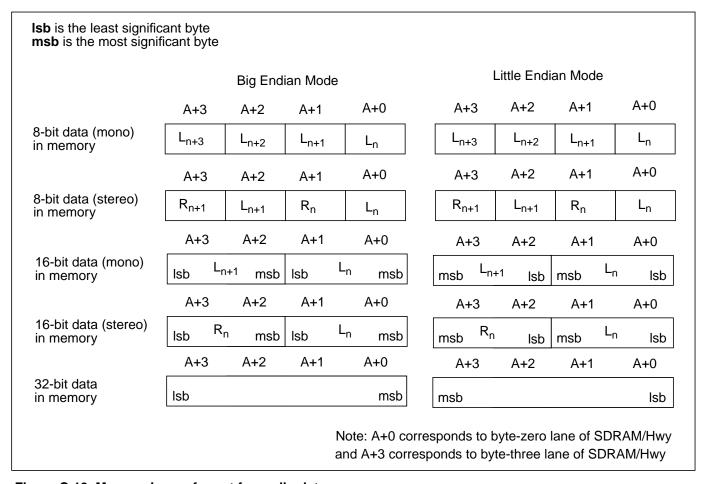

|   | 8.6 Memory Data Formats                             |      |

|   | 8.7 Audio In Operation                              |      |

|   | 8.8 Power Down and Sleepless                        |      |

|   | 8.9 Highway Latency and HBE                         |      |

|   | 8.10 Error Behavior                                 |      |

|   | 8.11 Diagnostic Mode                                |      |

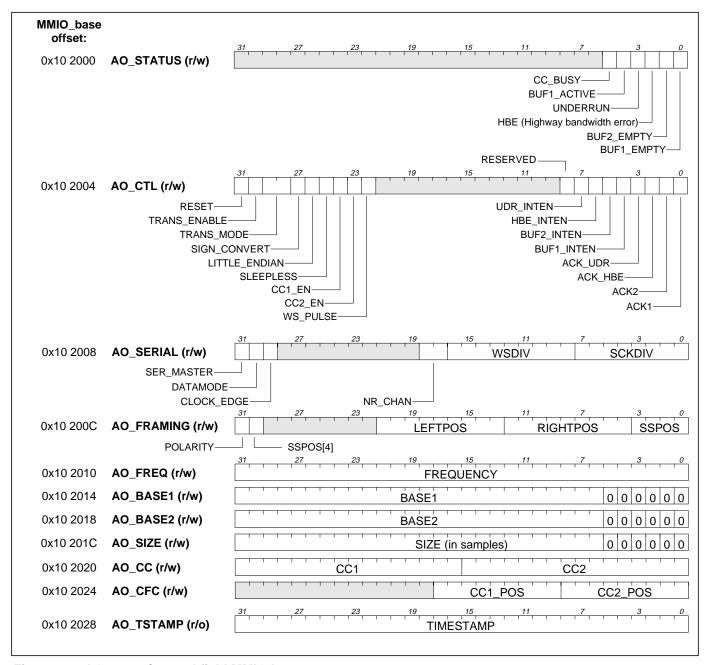

| 9 | Audio Out                                           |      |

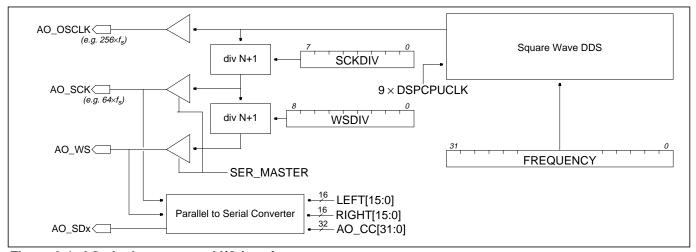

|   | 9.1 Audio Out Overview                              | 9-1  |

|   | 9.2 New and Changed Features                        |      |

|   | -                                                   |      |

|   | 9.5 External interface                              |      |

|   | 9.3 External Interface     9.4 Summary of Operation |      |

|    | 9.5 Internal Clock Source             | 9-2  |

|----|---------------------------------------|------|

|    | 9.5.1 TM1300 Standard Mode            | 9-2  |

|    | 9.5.2 TM1000 Clock Compatibility Mode | 9-3  |

|    | 9.6 Clock System Operation            | 9-3  |

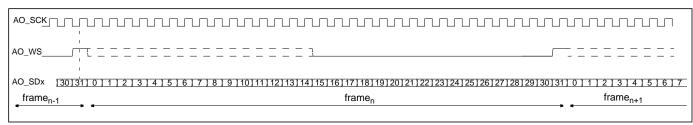

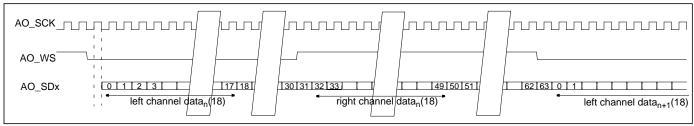

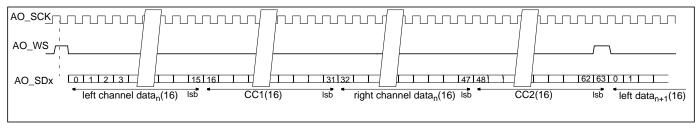

|    | 9.7 Serial Data Framing               | 9-3  |

|    | 9.7.1 Serial Frame Limitations        | 9-4  |

|    | 9.7.2 I2S Serial Framing Example      | 9-5  |

|    | 9.8 Codec Control                     | 9-5  |

|    | 9.9 Memory Data Formats               | 9-6  |

|    | 9.10 Audio Out Operation              | 9-7  |

|    | 9.11 Interrupts                       | 9-8  |

|    | 9.12 Timestamp                        | 9-9  |

|    | 9.13 powerdown and Sleepless          | 9-9  |

|    | 9.14 Highway Latency and HBE          | 9-9  |

|    | 9.15 Error Behavior                   | 9-10 |

| 40 | SPDIF Out                             |      |

| 10 |                                       |      |

|    | 10.1 SPDIF Out Overview               |      |

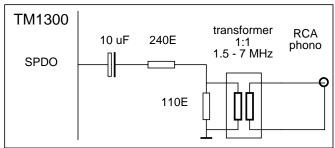

|    | 10.2 External Interface               |      |

|    | 10.3 Summary of Operation             |      |

|    | 10.3.1 SPDIF Mode                     |      |

|    | 10.3.2 Transparent DMA Mode           |      |

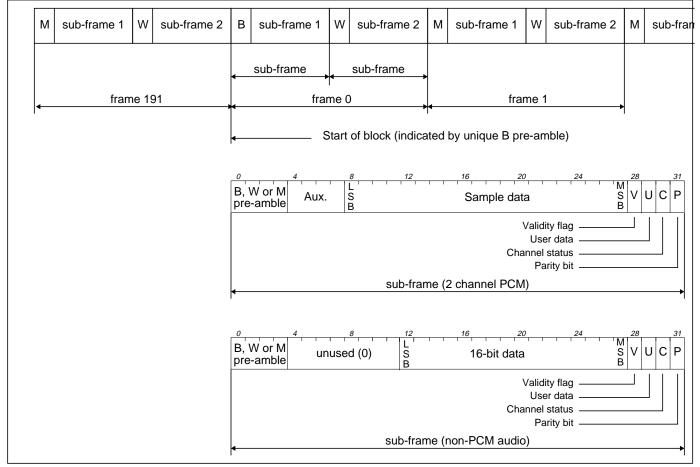

|    | 10.4 IEC-958 Serial Format            |      |

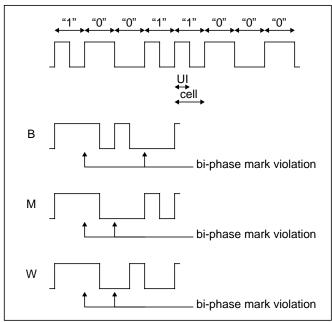

|    | 10.5 IEC-958 Bit Cell and Pre-amble   | _    |

|    | 10.6 IEC-958 Parity                   |      |

|    | 10.7 IEC-958 Memory Data Format       |      |

|    | 10.8 Sample Rate Programming          | 10-3 |

|    | 10.9 Transparent Mode                 |      |

|    | 10.10 DMA Operation                   |      |

|    | 10.11 DMA Error Conditions            |      |

|    | 10.12 Interrupts                      | 10-4 |

|    | 10.13 Timestamps                      |      |

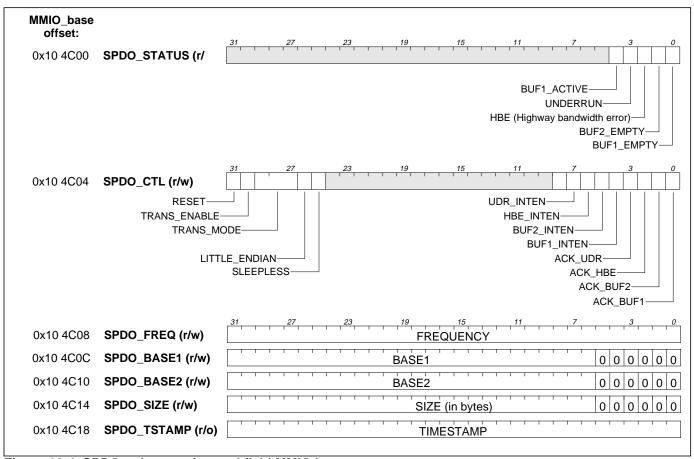

|    | 10.14 MMIO Register Description       | 10-5 |

|    | 10.15 RESET                           | 10-6 |

|    | 10.16 Power Down and Sleepless        | 10-6 |

|    | 10.17 HBE and Highway Latency         | 10-6 |

|    | 10.18 Literature References           | 10-7 |

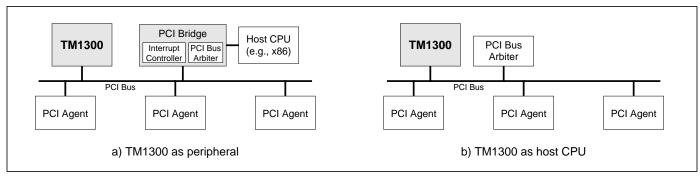

| 11 | PCI Interface                         |      |

|    | 11.1 New in TM1300                    | 11-1 |

|    | 11.2 PCI Overview                     | 11-1 |

|    |                                       |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -2                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| 11.3.1 DSPCPU Single-Word Loads/Stores                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -2                                                                   |

| 11.3.2 I/O Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -2                                                                   |

| 11.3.3 Configuration Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -2                                                                   |

| 11.3.4 DMA Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -2                                                                   |

| 11.4 PCI Interface as a Target                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -3                                                                   |

| 11.5 Transaction Concurrency, Priorities, and Ordering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -3                                                                   |

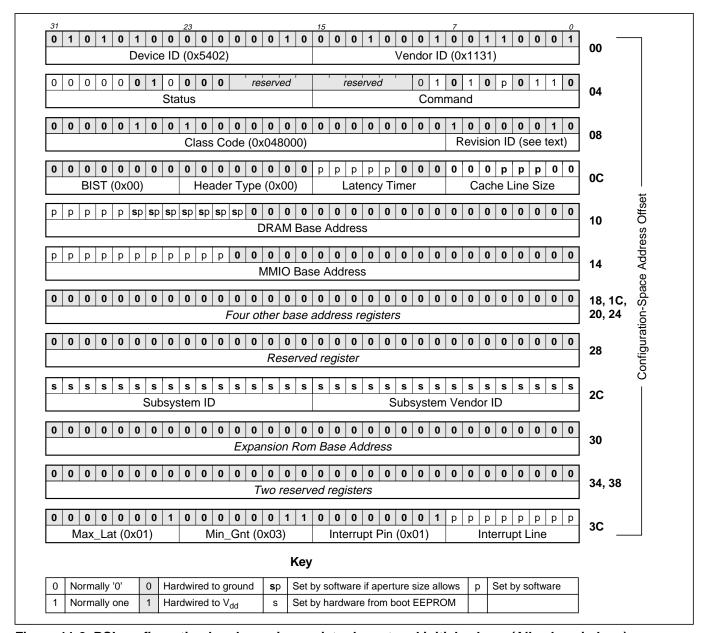

| 11.6 Registers Addressed in PCI Configuration Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -3                                                                   |

| 11.6.1 Vendor ID Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -3                                                                   |

| 11.6.2 Device ID Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -3                                                                   |

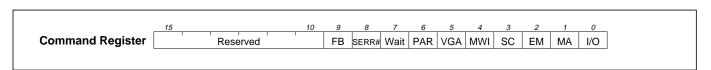

| 11.6.3 Command Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -3                                                                   |

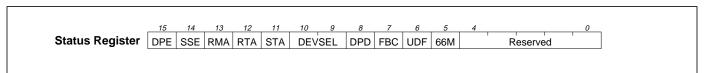

| 11.6.4 Status Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -5                                                                   |

| 11.6.5 Revision ID Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -6                                                                   |

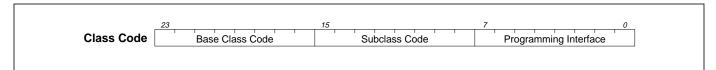

| 11.6.6 Class Code Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -6                                                                   |

| 11.6.7 Cache Line Size Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -6                                                                   |

| 11.6.8 Latency Timer Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -7                                                                   |

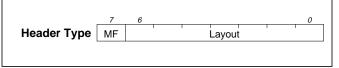

| 11.6.9 Header Type Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -7                                                                   |

| 11.6.10 Built-In Self Test Register11-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -7                                                                   |

| 11.6.11 Base Address Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -7                                                                   |

| 11.6.12 Subsystem ID, Subsystem Vendor ID Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -8                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                      |

| 11.6.13 Expansion ROM Base Address Register11-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -9                                                                   |

| 11.6.13 Expansion ROM Base Address Register    11.6.14 Interrupt Line Register    11.6.14 Interrupt Line Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                      |

| · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -9                                                                   |

| 11.6.14 Interrupt Line Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -9<br>-9                                                             |

| 11.6.14 Interrupt Line Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -9<br>-9<br>-9                                                       |

| 11.6.14 Interrupt Line Register11-11.6.15 Interrupt Pin Register11-11.6.16 Max_Lat, Min_Gnt Registers11-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -9<br>-9<br>-9                                                       |

| 11.6.14 Interrupt Line Register11-11.6.15 Interrupt Pin Register11-11.6.16 Max_Lat, Min_Gnt Registers11-11.7 Registers in MMIO Space11-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -9<br>-9<br>-9<br>-9                                                 |

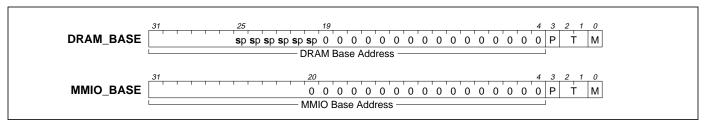

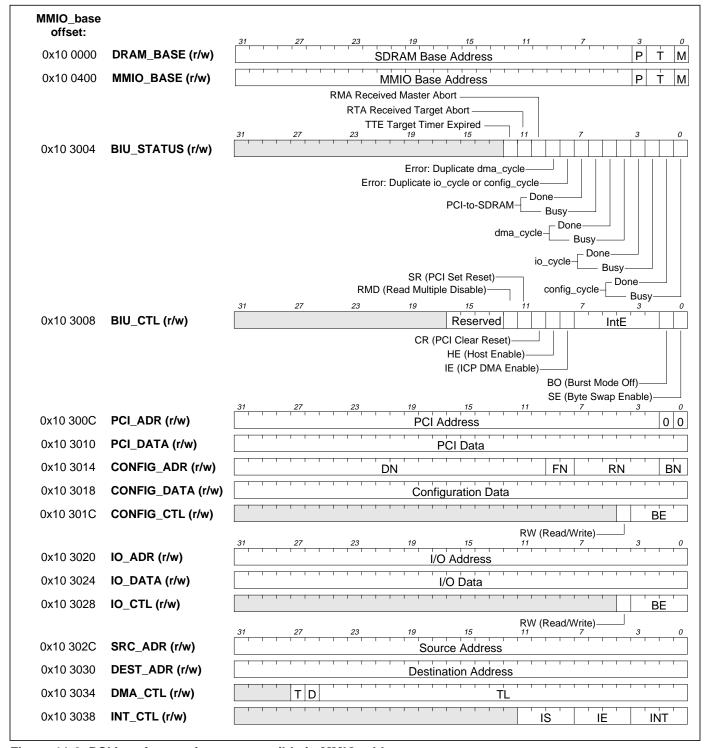

| 11.6.14 Interrupt Line Register       11-         11.6.15 Interrupt Pin Register       11-         11.6.16 Max_Lat, Min_Gnt Registers       11-         11.7 Registers in MMIO Space       11-         11.7.1 DRAM_BASE Register       11-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -9<br>-9<br>-9<br>-9<br>-9                                           |

| 11.6.14 Interrupt Line Register       11-         11.6.15 Interrupt Pin Register       11-         11.6.16 Max_Lat, Min_Gnt Registers       11-         11.7 Registers in MMIO Space       11-         11.7.1 DRAM_BASE Register       11-         11.7.2 MMIO_BASE Register       11-                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -9<br>-9<br>-9<br>-9<br>-9                                           |

| 11.6.14 Interrupt Line Register       11-         11.6.15 Interrupt Pin Register       11-         11.6.16 Max_Lat, Min_Gnt Registers       11-         11.7 Registers in MMIO Space       11-         11.7.1 DRAM_BASE Register       11-         11.7.2 MMIO_BASE Register       11-         11.7.3 MMIO/DRAM_BASE updates       11-                                                                                                                                                                                                                                                                                                                                                                                                        | -9<br>-9<br>-9<br>-9<br>-9<br>-9                                     |

| 11.6.14 Interrupt Line Register       11-         11.6.15 Interrupt Pin Register       11-         11.6.16 Max_Lat, Min_Gnt Registers       11-         11.7 Registers in MMIO Space       11-         11.7.1 DRAM_BASE Register       11-         11.7.2 MMIO_BASE Register       11-         11.7.3 MMIO/DRAM_BASE updates       11-         11.7.4 BIU_STATUS Register       11-                                                                                                                                                                                                                                                                                                                                                           | -9<br>-9<br>-9<br>-9<br>-9<br>-9<br>-10                              |

| 11.6.14 Interrupt Line Register       11-         11.6.15 Interrupt Pin Register       11-         11.6.16 Max_Lat, Min_Gnt Registers       11-         11.7 Registers in MMIO Space       11-         11.7.1 DRAM_BASE Register       11-         11.7.2 MMIO_BASE Register       11-         11.7.3 MMIO/DRAM_BASE updates       11-         11.7.4 BIU_STATUS Register       11-         11.7.5 BIU_CTL Register       11-                                                                                                                                                                                                                                                                                                                 | -9<br>-9<br>-9<br>-9<br>-9<br>-9<br>-10<br>-11                       |

| 11.6.14 Interrupt Line Register       11-         11.6.15 Interrupt Pin Register       11-         11.6.16 Max_Lat, Min_Gnt Registers       11-         11.7 Registers in MMIO Space       11-         11.7.1 DRAM_BASE Register       11-         11.7.2 MMIO_BASE Register       11-         11.7.3 MMIO/DRAM_BASE updates       11-         11.7.4 BIU_STATUS Register       11-         11.7.5 BIU_CTL Register       11-         11.7.6 PCI_ADR Register       11-                                                                                                                                                                                                                                                                       | -9<br>-9<br>-9<br>-9<br>-9<br>-10<br>-11<br>-12                      |

| 11.6.14 Interrupt Line Register       11-         11.6.15 Interrupt Pin Register       11-         11.6.16 Max_Lat, Min_Gnt Registers       11-         11.7 Registers in MMIO Space       11-         11.7.1 DRAM_BASE Register       11-         11.7.2 MMIO_BASE Register       11-         11.7.3 MMIO/DRAM_BASE updates       11-         11.7.4 BIU_STATUS Register       11-         11.7.5 BIU_CTL Register       11-         11.7.6 PCI_ADR Register       11-         11.7.7 PCI_DATA Register       11-                                                                                                                                                                                                                            | -9<br>-9<br>-9<br>-9<br>-9<br>-10<br>-11<br>-12<br>-12               |

| 11.6.14 Interrupt Line Register       11-         11.6.15 Interrupt Pin Register       11-         11.6.16 Max_Lat, Min_Gnt Registers       11-         11.7 Registers in MMIO Space       11-         11.7.1 DRAM_BASE Register       11-         11.7.2 MMIO_BASE Register       11-         11.7.3 MMIO/DRAM_BASE updates       11-         11.7.4 BIU_STATUS Register       11-         11.7.5 BIU_CTL Register       11-         11.7.6 PCI_ADR Register       11-         11.7.7 PCI_DATA Register       11-         11.7.8 CONFIG_ADR Register       11-                                                                                                                                                                               | -9<br>-9<br>-9<br>-9<br>-9<br>-10<br>-11<br>-12<br>-12               |

| 11.6.14 Interrupt Line Register       11-         11.6.15 Interrupt Pin Register       11-         11.6.16 Max_Lat, Min_Gnt Registers       11-         11.7 Registers in MMIO Space       11-         11.7.1 DRAM_BASE Register       11-         11.7.2 MMIO_BASE Register       11-         11.7.3 MMIO/DRAM_BASE updates       11-         11.7.4 BIU_STATUS Register       11-         11.7.5 BIU_CTL Register       11-         11.7.6 PCI_ADR Register       11-         11.7.7 PCI_DATA Register       11-         11.7.8 CONFIG_ADR Register       11-         11.7.9 CONFIG_DATA Register       11-         11.7.9 CONFIG_DATA Register       11-                                                                                   | -9<br>-9<br>-9<br>-9<br>-9<br>-10<br>-12<br>-12<br>-12<br>-13        |

| 11.6.14 Interrupt Line Register       11-         11.6.15 Interrupt Pin Register       11-         11.6.16 Max_Lat, Min_Gnt Registers       11-         11.7 Registers in MMIO Space       11-         11.7.1 DRAM_BASE Register       11-         11.7.2 MMIO_BASE Register       11-         11.7.3 MMIO/DRAM_BASE updates       11-         11.7.4 BIU_STATUS Register       11-         11.7.5 BIU_CTL Register       11-         11.7.6 PCI_ADR Register       11-         11.7.7 PCI_DATA Register       11-         11.7.9 CONFIG_ADR Register       11-         11.7.9 CONFIG_DATA Register       11-         11.7.10 CONFIG_CTL Register       11-                                                                                   | -9<br>-9<br>-9<br>-9<br>-9<br>-10<br>-11<br>-12<br>-12<br>-13<br>-13 |

| 11.6.14 Interrupt Line Register       11-         11.6.15 Interrupt Pin Register       11-         11.6.16 Max_Lat, Min_Gnt Registers       11-         11.7 Registers in MMIO Space       11-         11.7.1 DRAM_BASE Register       11-         11.7.2 MMIO_BASE Register       11-         11.7.3 MMIO/DRAM_BASE updates       11-         11.7.4 BIU_STATUS Register       11-         11.7.5 BIU_CTL Register       11-         11.7.6 PCI_ADR Register       11-         11.7.7 PCI_DATA Register       11-         11.7.9 CONFIG_ADR Register       11-         11.7.10 CONFIG_CTL Register       11-         11.7.11 IO_ADR Register       11-         11.7.11 IO_ADR Register       11-                                             | -9<br>-9<br>-9<br>-9<br>-9<br>-10<br>-12<br>-12<br>-12<br>-13<br>-13 |

| 11.6.14 Interrupt Line Register       11-         11.6.15 Interrupt Pin Register       11-         11.6.16 Max_Lat, Min_Gnt Registers       11-         11.7 Registers in MMIO Space       11-         11.7.1 DRAM_BASE Register       11-         11.7.2 MMIO_BASE Register       11-         11.7.3 MMIO/DRAM_BASE updates       11-         11.7.4 BIU_STATUS Register       11-         11.7.5 BIU_CTL Register       11-         11.7.6 PCI_ADR Register       11-         11.7.7 PCI_DATA Register       11-         11.7.9 CONFIG_ADR Register       11-         11.7.10 CONFIG_CTL Register       11-         11.7.11 IO_ADR Register       11-         11.7.12 IO_DATA Register       11-         11.7.12 IO_DATA Register       11- | -9<br>-9<br>-9<br>-9<br>-9<br>-10<br>-12<br>-12<br>-13<br>-13<br>-13 |

|    | 11.7.16 DMA_CTL Register                       | 11-14 |

|----|------------------------------------------------|-------|

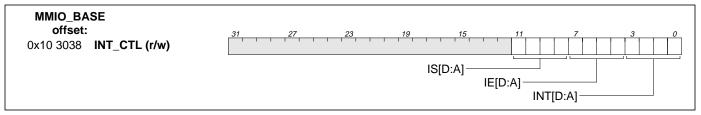

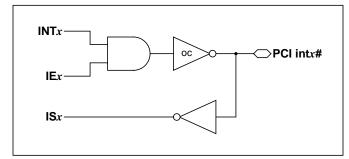

|    | 11.7.17 INT_CTL Register                       | 11-15 |

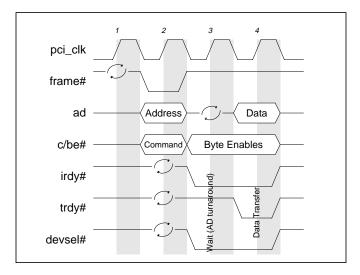

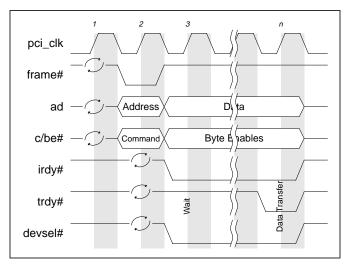

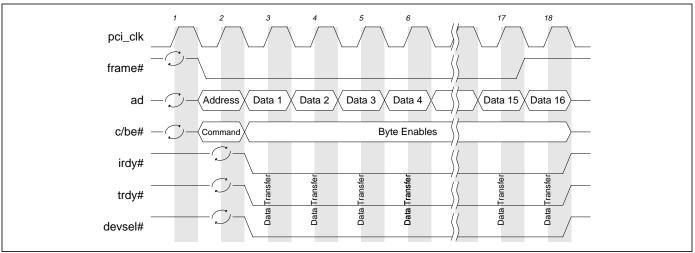

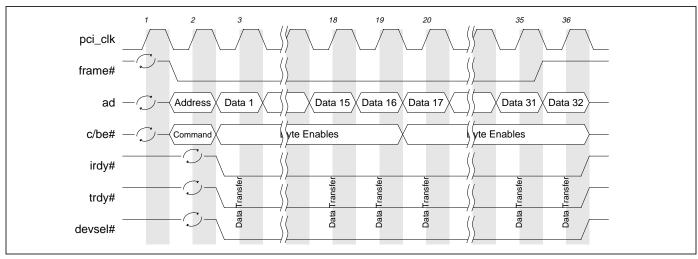

|    | 11.8 PCI Bus Protocol Overview                 | 11-15 |

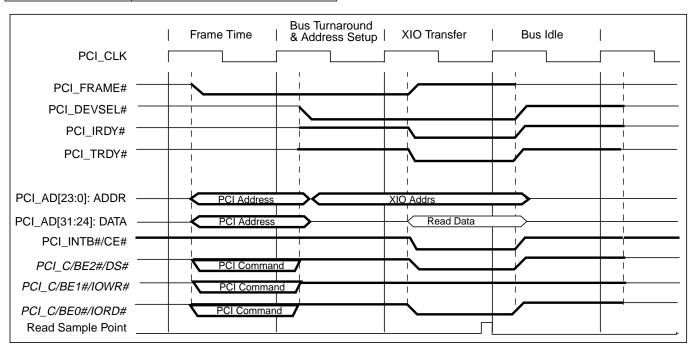

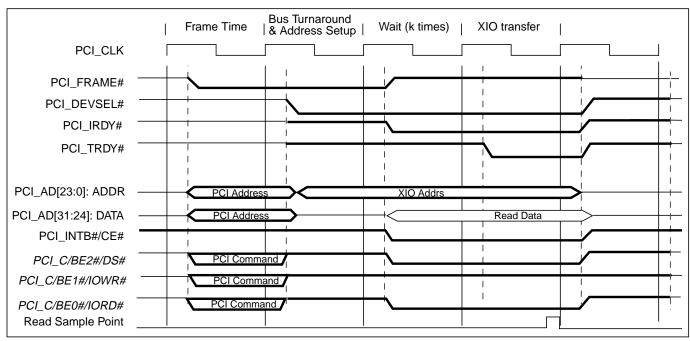

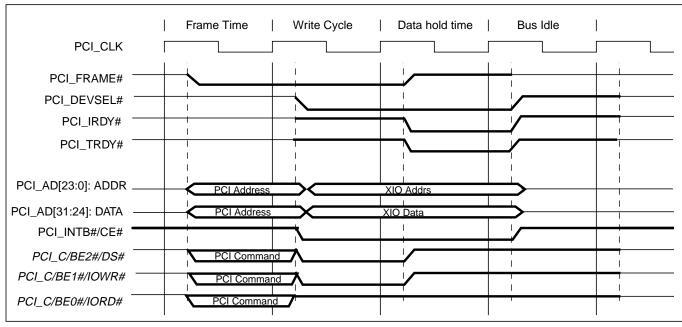

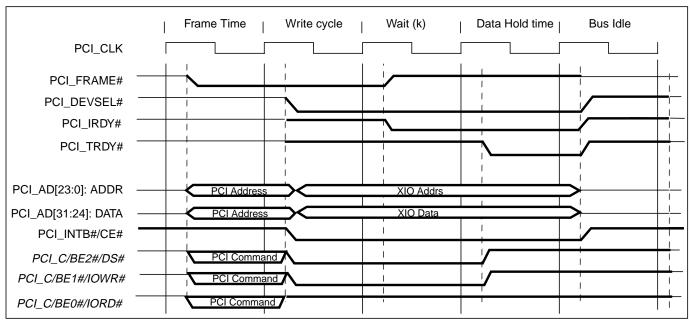

|    | 11.8.1 Single-Data-Phase Operations            | 11-15 |

|    | 11.8.2 Multi-Data-Phase Operations             | 11-16 |

|    | 11.9 Limitations                               | 11-17 |

|    | 11.9.1 Bus Locking                             | 11-17 |

|    | 11.9.2 No Expansion ROM                        | 11-17 |

|    | 11.9.3 No Cacheline Wrap Address Sequence      | 11-17 |

|    | 11.9.4 No Burst for I/O or Configuration Space | 11-17 |

|    | 11.9.5 Word-Only MMIO Register Access          | 11-17 |

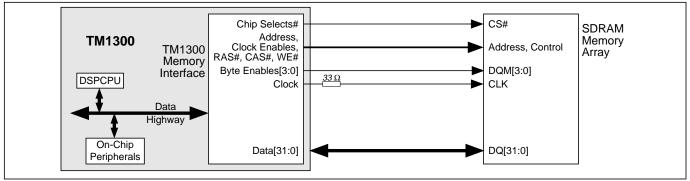

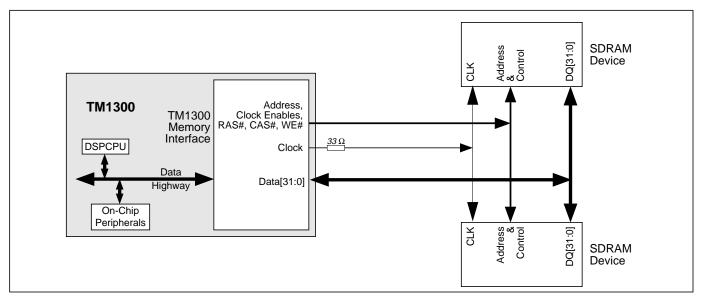

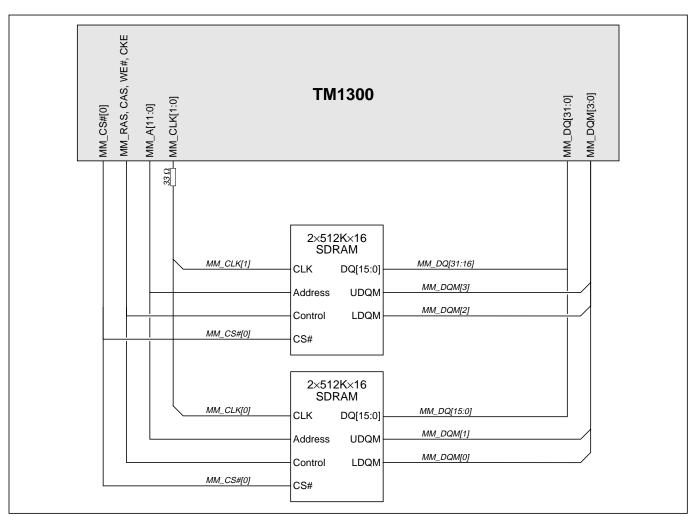

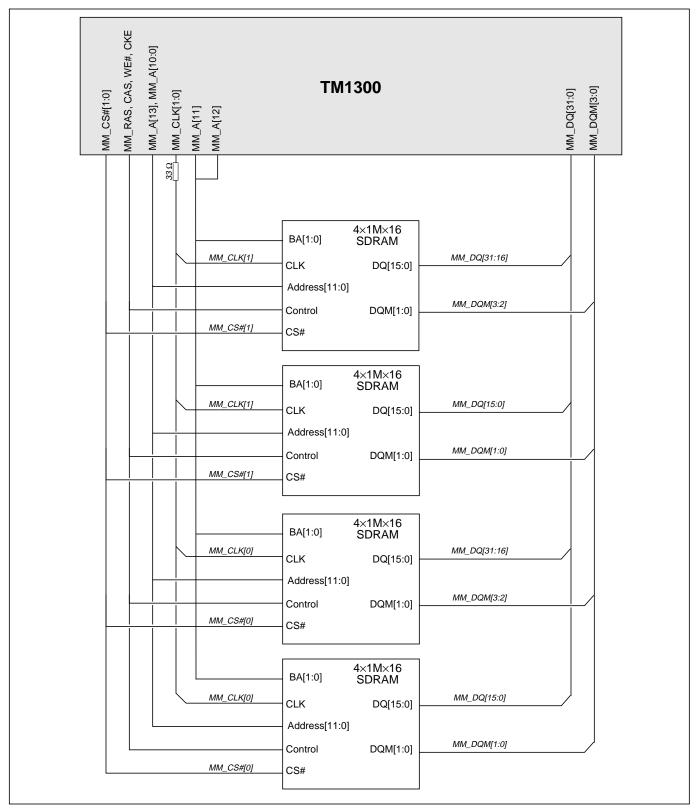

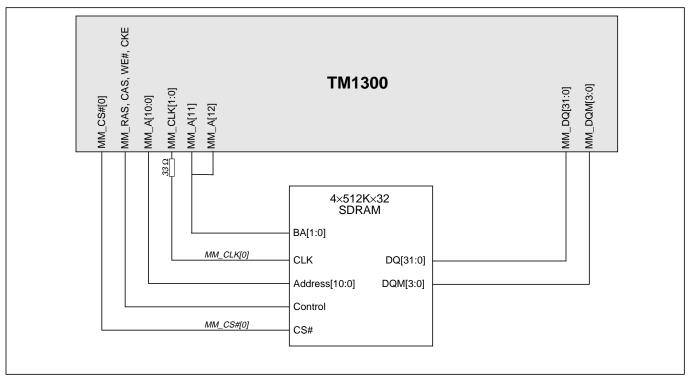

| 12 | SDRAM Memory System                            |       |

|    | 12.1 New in TM1300                             | 12-1  |

|    | 12.2 TM1300 Main Memory Overview               | 12-1  |

|    | 12.3 Main-Memory Address Aperture              | 12-1  |

|    | 12.4 Memory Devices Supported                  | 12-2  |

|    | 12.4.1 SDRAM                                   | 12-2  |

|    | 12.4.2 SGRAM                                   | 12-2  |

|    | 12.5 Memory Granularity and Sizes              | 12-2  |

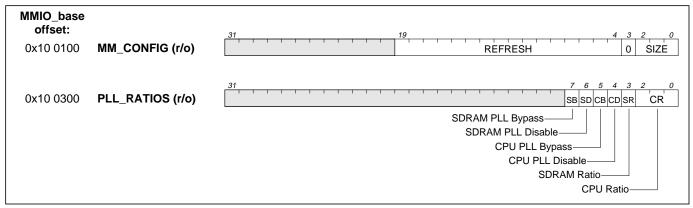

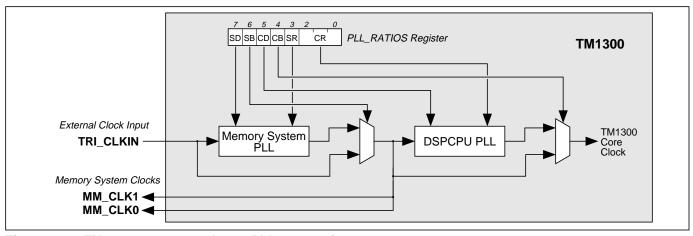

|    | 12.6 Memory System Programming                 | 12-3  |

|    | 12.6.1 MM_CONFIG Register                      | 12-3  |

|    | 12.6.2 PLL_RATIOS Register                     | 12-3  |

|    | 12.7 Memory Interface Pin List                 | 12-5  |

|    | 12.8 Address Mapping                           | 12-5  |

|    | 12.9 Memory Interface and SDRAM Initialization | 12-5  |

|    | 12.10 On-Chip SDRAM Interleaving               | 12-5  |

|    | 12.11 Refresh                                  | 12-6  |

|    | 12.12 Power-Down Mode                          | 12-6  |

|    | 12.13 Output Driver Capacity                   | 12-6  |

|    | 12.14 Signal Propagation Delay Compensation    | 12-6  |

|    | 12.15 Circuit Board Design                     | 12-6  |

|    | 12.15.1 General Guidelines                     | 12-6  |

|    | 12.15.2 Specific Guidelines                    | 12-7  |

|    | 12.15.3 Termination                            | 12-7  |

|    | 12.16 Timing Budget                            | 12-7  |

|    | 12.16.1 Main AC Parameter requirements         | 12-8  |

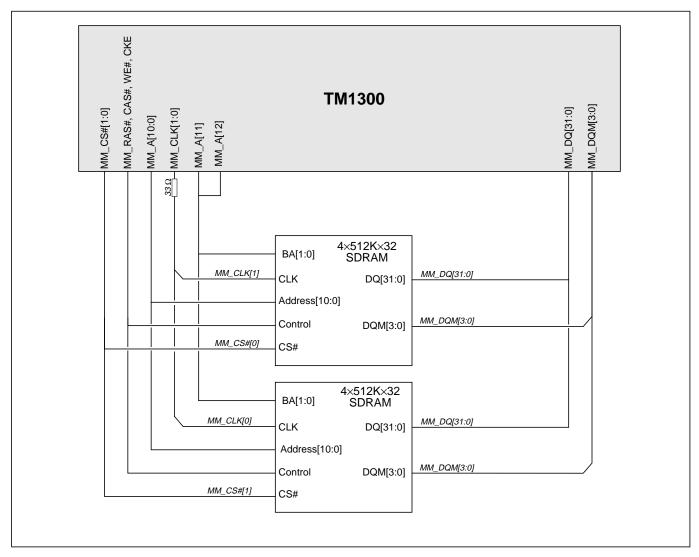

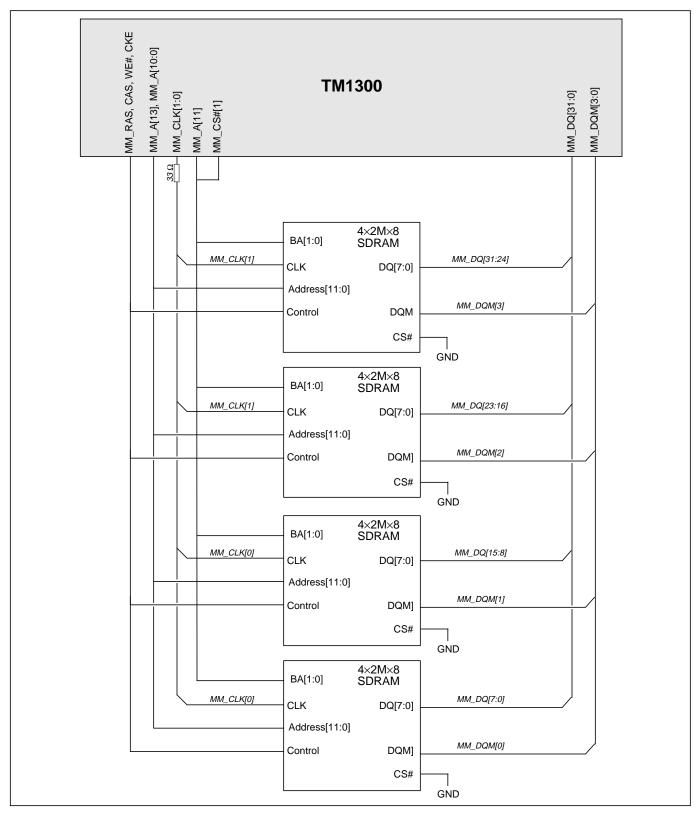

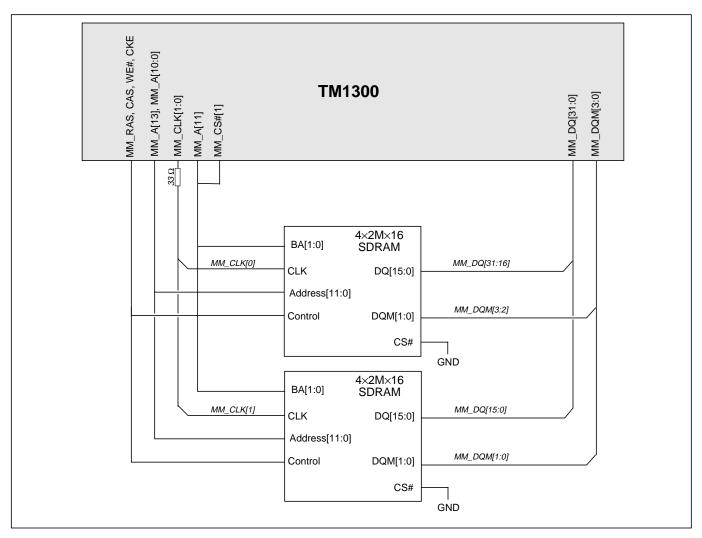

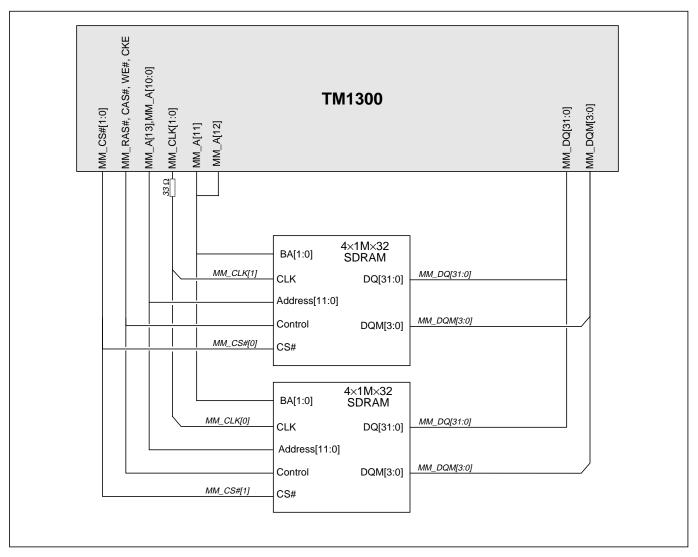

|    | 12.17 Example Block Diagrams                   | 12-8  |

|    | 12.17.1 16-Mbit Devices or Less                | 12-8  |

|    | 12.17.2 64-Mbit Devices                        | 12-8  |

|    | 12.17.3 128-Mbit Devices                       | 12-12 |

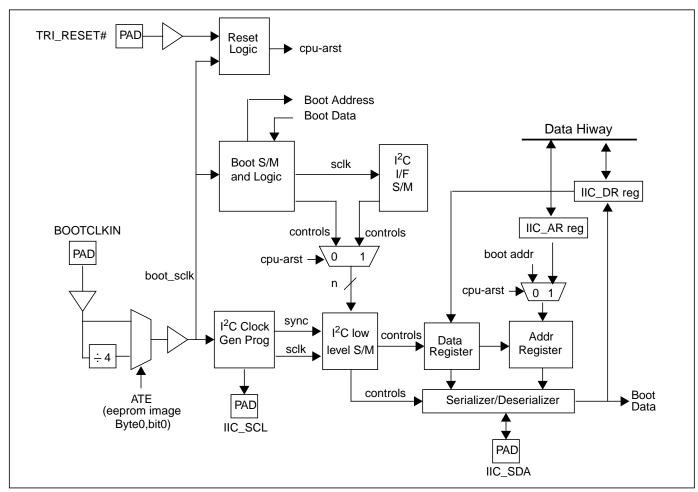

## 13 System Boot

|    | 13.1 New in TM1300                                                          |

|----|-----------------------------------------------------------------------------|

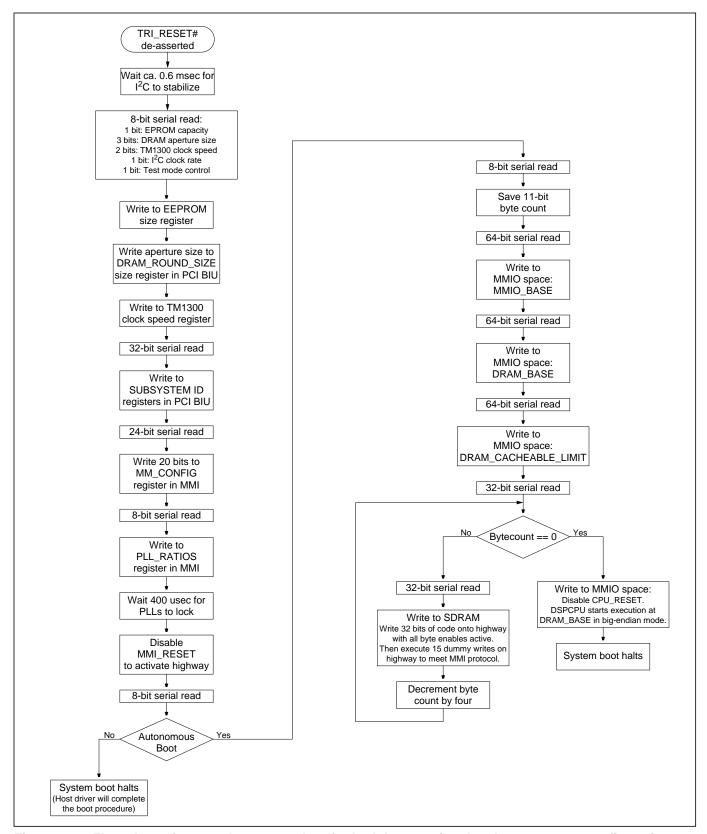

|    | 13.2 TM1300 Boot Sequence Overview                                          |

|    | 13.3 Boot Hardware Operation                                                |

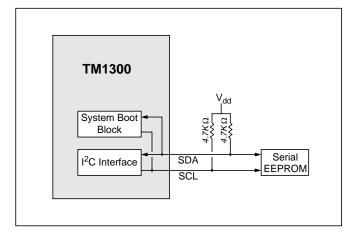

|    | 13.3.1 Boot Procedure Common to Both Autonomous and Host-Assisted Bootstrap |

|    | 13.3.2 Initial DSPCPU Program Load for Autonomous Bootstrap                 |

|    | 13.4 Host-Assisted Boot Description                                         |

|    | 13.4.1 Stage 1: TM1300 System Boot Hardware                                 |

|    | 13.4.2 Stage 2: Host-System PCI Configuration                               |

|    | 13.4.3 Stage 3: TM1300 Driver Executing on the Host                         |

|    | 13.5 Detailed EEPROM Contents                                               |

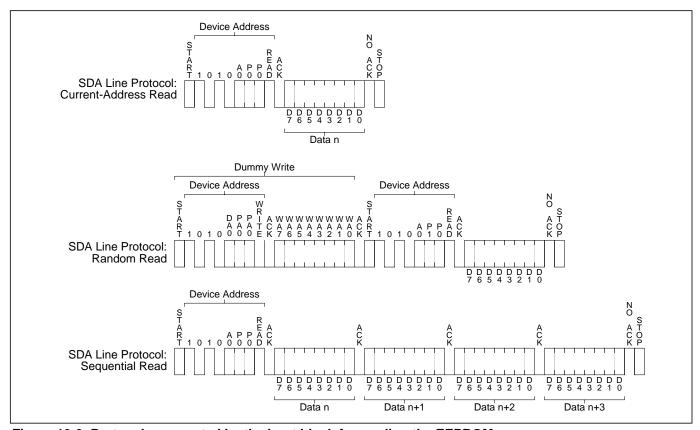

|    | 13.6 EEPROM Access Protocols                                                |

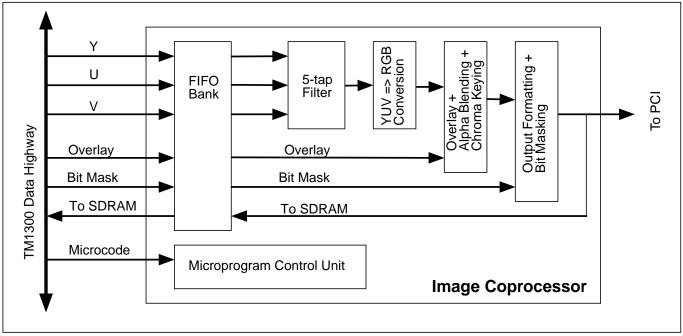

| 14 | Image Coprocessor                                                           |

|    | 14.1 Image Coprocessor Overview                                             |

|    | 14.2 Requirements                                                           |

|    | 14.2.1 Functions                                                            |

|    | 14.2.2 Bandwidth                                                            |

|    | 14.2.3 Image Size and Scaling                                               |

|    | 14.3 Interface                                                              |

|    | 14.4 Data Formats                                                           |

|    | 14.4.1 Image Input Formats                                                  |

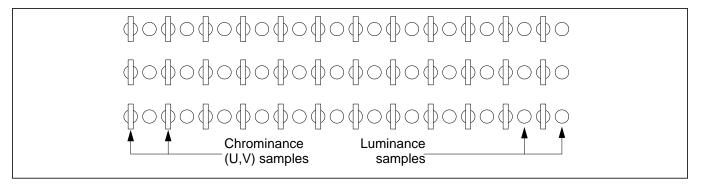

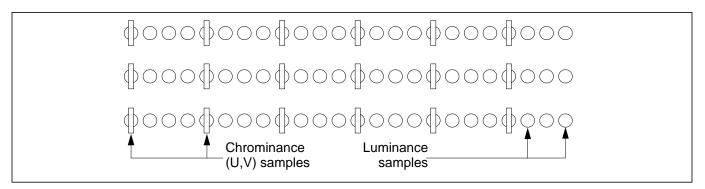

|    | 14.4.1.1 YUV 4:2:2 Co-Sited                                                 |

|    | 14.4.1.2 YUV 4:2:2 Interspersed                                             |

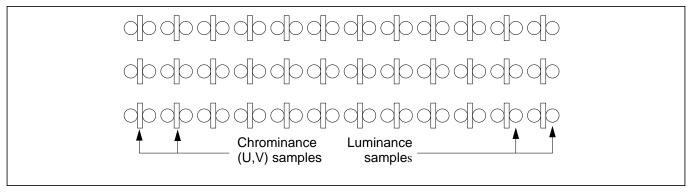

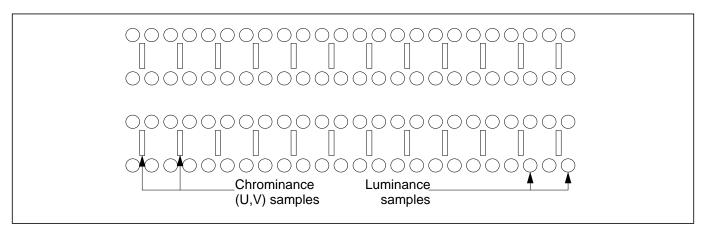

|    | 14.4.1.3 YUV 4:2:0 XY Interspersed                                          |

|    | 14.4.1.4 YUV 4:1:1 Co-Sited                                                 |

|    | 14.4.2 Image Overlay Formats                                                |

|    | 14.4.3 Alpha Blending Codes                                                 |

|    | 14.4.4 Output Formats                                                       |

|    | 14.5 Algorithms                                                             |

|    | 14.5.1 Introduction                                                         |

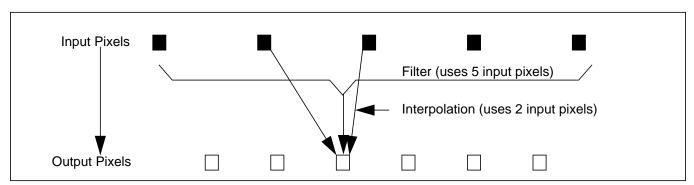

|    | 14.5.2 Filtering                                                            |

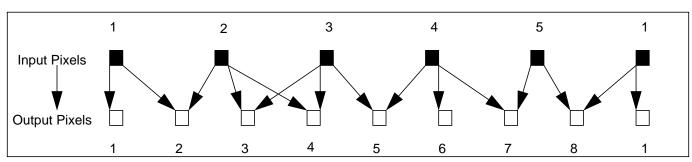

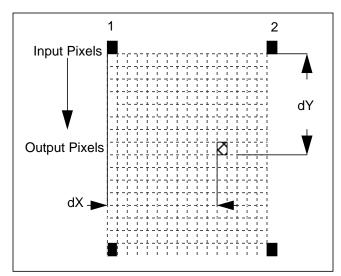

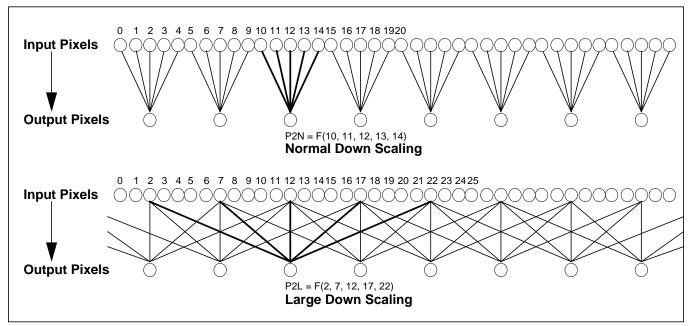

|    | 14.5.3 Scaling                                                              |

|    | 14.5.4 YUV to RGB Conversion                                                |

|    | 14.5.5 Overlay and Alpha Blending                                           |

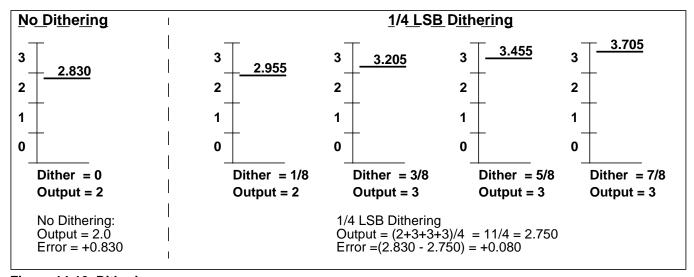

|    | 14.5.6 Dithering                                                            |

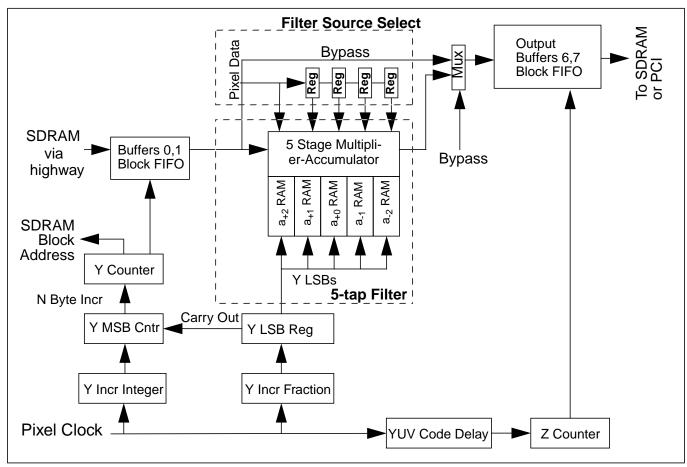

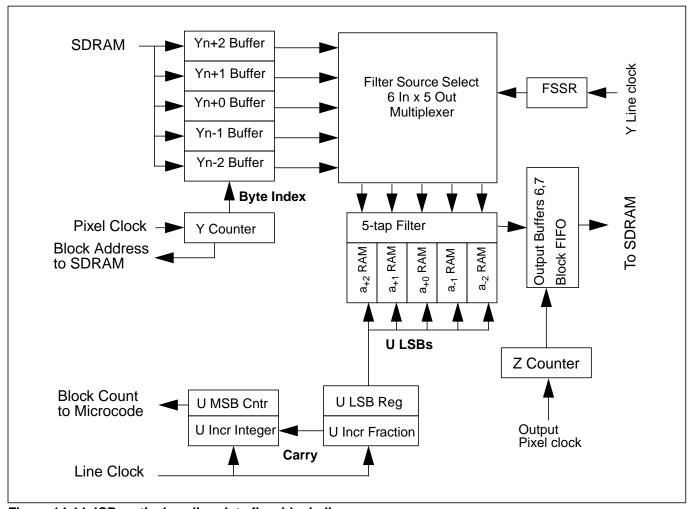

|    | 14.5.7 Implementation Overview: Horizontal Scaling and Filtering            |

|    | 14.5.7.1 Loading the extra pixels in the filter                             |

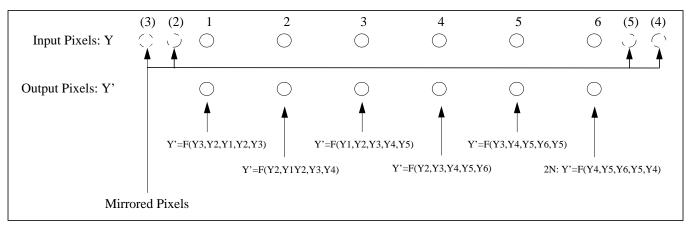

|    | 14.5.7.2 Mirroring pixels at the ends of a line                             |

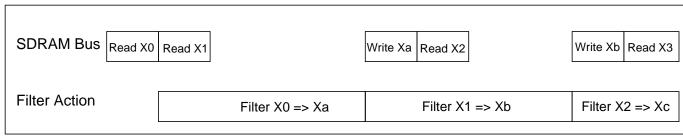

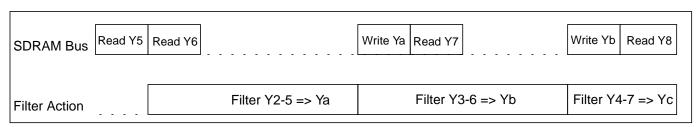

|    | 14.5.7.3 Horizontal filter SDRAM timing                                     |

|    |                                                                             |

|     | 14.5.8 Implementation Overview: Vertical Scaling and Filtering    | 12 |

|-----|-------------------------------------------------------------------|----|

|     | 14.5.8.1 Mirroring lines at the ends of an image                  |    |

|     | 14.5.8.2 Vertical filter SDRAM block timing                       |    |

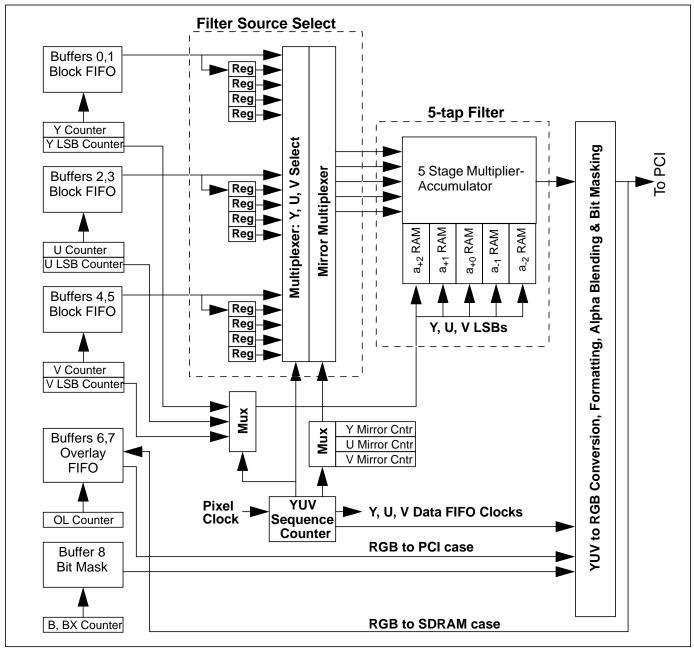

|     | 14.5.9 Horizontal Scaling and Filtering for RGB Output            |    |

|     | 14.5.9.1 YUV sequence counter in YUV 4:2:2 output Mode            |    |

|     | 14.5.9.2 PCI output block timing                                  |    |

|     | 14.6 Operation and Programming                                    |    |

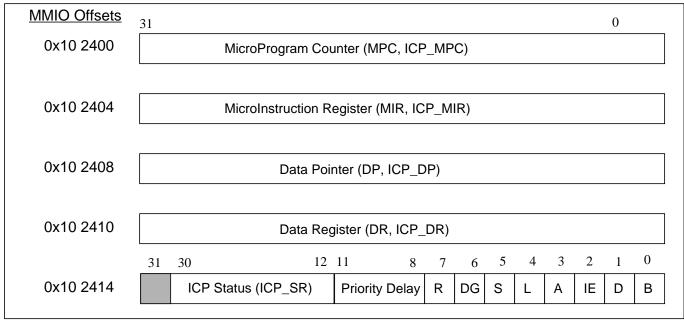

|     | 14.6.1 ICP Register Model                                         |    |

|     | 14.6.2 Power Down                                                 |    |

|     | 14.6.3 ICP Operation                                              |    |

|     | 14.6.4 ICP Microprogram Set                                       |    |

|     | 14.6.5 ICP Processing Time                                        |    |

|     | 14.6.6 Priority Delay and ICP Minimum Bus Bandwidth               |    |

|     | 14.6.7 ICP Parameter Tables                                       |    |

|     | 14.6.8 Load Coefficients                                          | 22 |

|     | 14.6.9 Horizontal Filter - SDRAM to SDRAM                         | 22 |

|     | 14.6.9.1 Algorithms                                               | 22 |

|     | 14.6.9.2 Parameter table                                          | 22 |

|     | 14.6.9.3 Control word format                                      | 23 |

|     | 14.6.10 Vertical Filter - SDRAM to SDRAM                          | 24 |

|     | 14.6.10.1 Algorithms                                              | 24 |

|     | 14.6.10.2 Parameter table                                         | 24 |

|     | 14.6.10.3 Control word format                                     | 25 |

|     | 14.6.11 Horizontal Filter with RGB/YUV Conversion to PCI or SDRAM | 25 |

|     | 14.6.11.1 Algorithms                                              | 25 |

|     | 14.6.11.2 Parameter table                                         | 26 |

|     | 14.6.11.3 Control word format                                     | 27 |

| 4 E | Variable Langth Deceder                                           |    |

| 13  | Variable Length Decoder                                           |    |

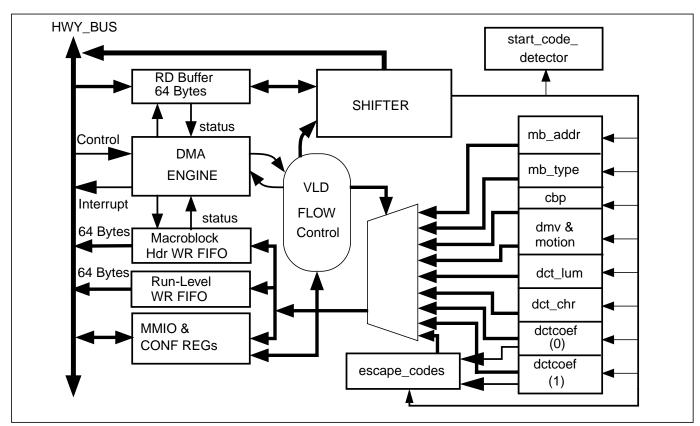

|     | 15.1 VLD Overview                                                 |    |

|     | 15.2 VLD Operation                                                |    |

|     | 15.3 Decoding up to A slice                                       |    |

|     | 15.4 VLD Input                                                    |    |

|     | 15.5 VLD Output                                                   |    |

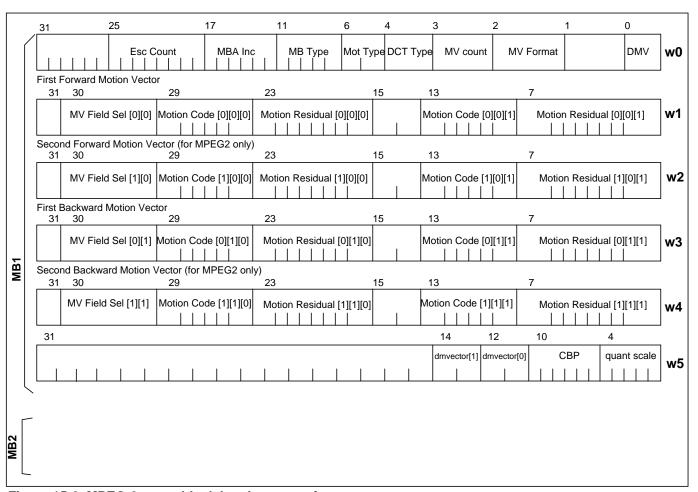

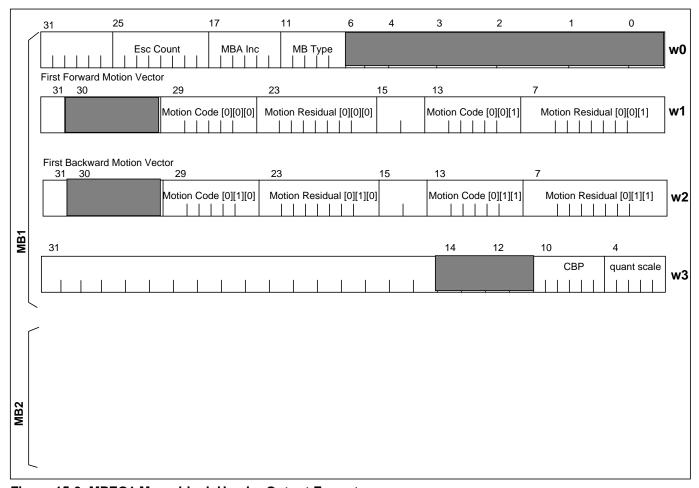

|     | 15.5.1 Macroblock Header Output Data                              |    |

|     | 15.5.2 Run-Level Output Data                                      |    |

|     | 15.6 VLD Time Sharing                                             |    |

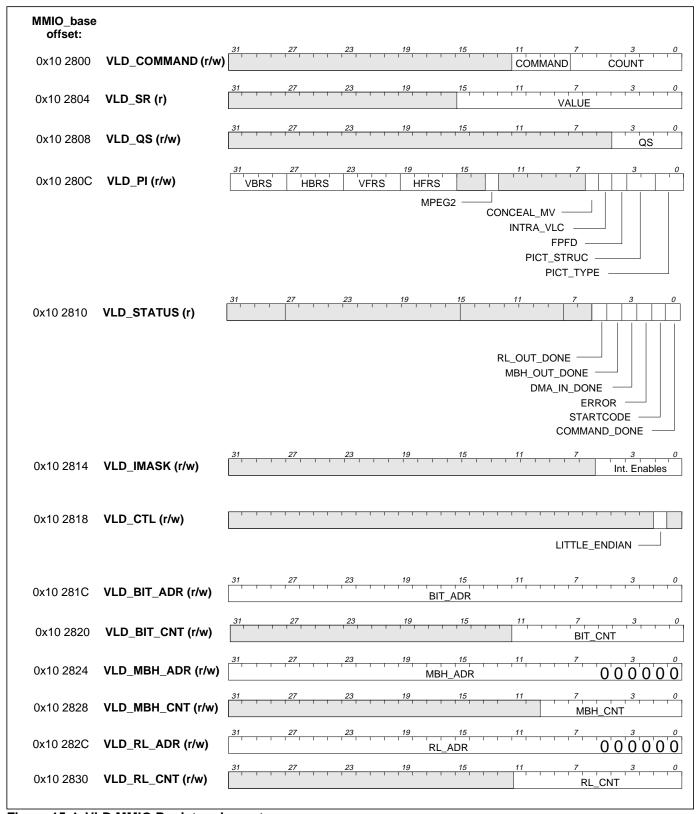

|     | 15.7 MMIO Registers                                               |    |

|     | 15.7.1 VLD Status (VLD_STATUS)                                    |    |

|     | 15.7.2 VLD Interrupt Enable (VLD_IMASK)                           |    |

|     | 15.7.3 VLD Control (VLD_CTL)                                      | วี |

|     | 15.8 VLD DMA Registers                     |

|-----|--------------------------------------------|

|     | 15.8.1 DMA Input                           |

|     | 15.8.2 Macroblock Header Output DMA        |

|     | 15.8.3 Run-Level Output DMA                |

|     | 15.9 VLD Operational Registers             |

|     | 15.9.1 VLD Command (VLD_COMMAND)           |

|     | 15.9.2 VLD Shift Register (VLD_SR)         |

|     | 15.9.3 VLD Quantizer Scale (VLD_QS)        |

|     | 15.9.4 VLD Picture Info (VLD_PI)           |

|     | 15.10 Error Handling                       |

|     | 15.11 Interrupt                            |

|     | 15.12 RESET                                |

|     | 15.13 Endian-ness                          |

|     | 15.14 Power Down                           |

|     | 15.15 References                           |

| 40  |                                            |

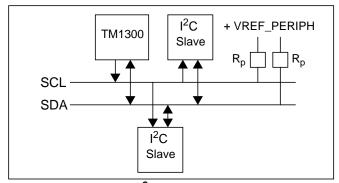

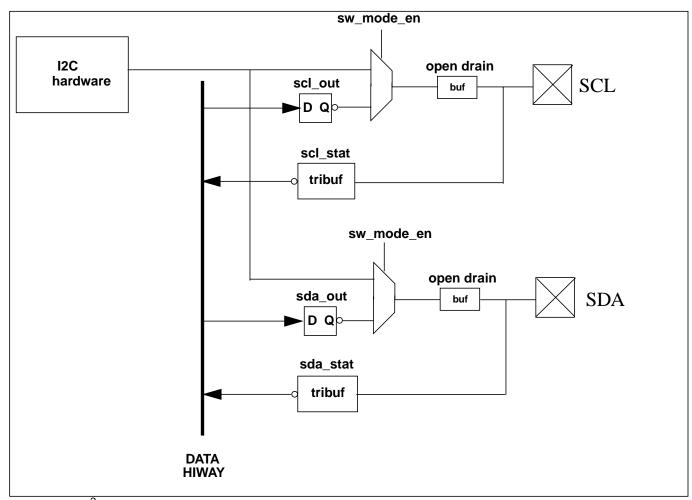

| 16  | I2C Interface                              |

|     | 16.1 I2C Overview                          |

|     | 16.2 New in TM1300                         |

|     | 16.3 External Interface                    |

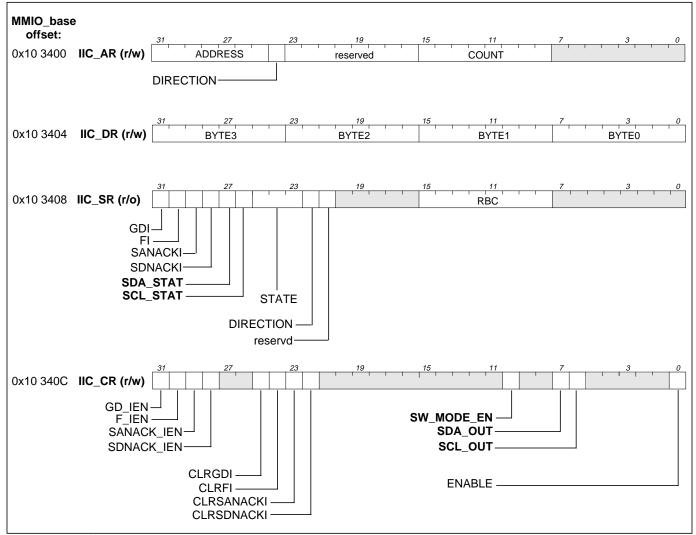

|     | 16.4 I2C Register Set                      |

|     | 16.4.1 IIC_AR Register                     |

|     | 16.4.2 IIC_DR Register                     |

|     | 16.4.3 IIC_SR Register                     |

|     | 16.4.4 IIC_CR Register                     |

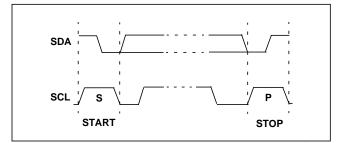

|     | 16.5 I2C Software Operation Mode           |

|     | 16.6 I2C Hardware Operation Mode           |

|     | 16.6.1 Slave NAK                           |

|     | 16.7 I2C Clock Rate Generation             |

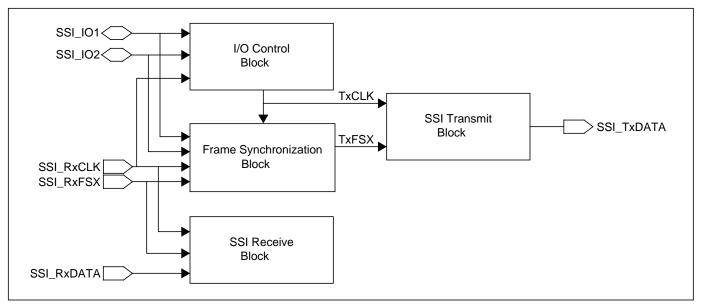

| 17  | Synchronous Sorial Interface               |

| 1 / | Synchronous Serial Interface               |

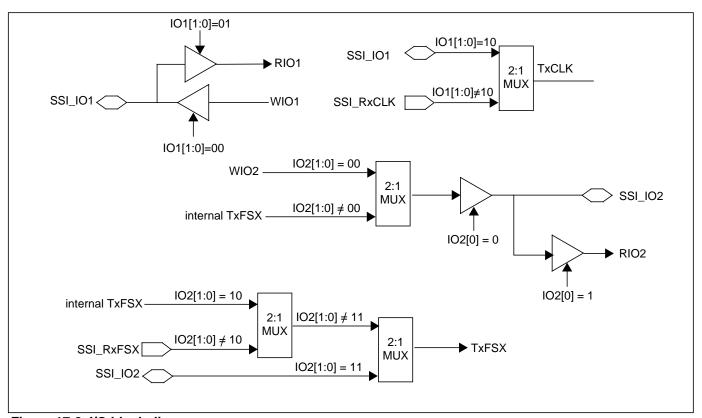

|     | 17.1 Synchronous Serial Interface Overview |

|     | 17.2 Interface                             |

|     | 17.3 Block Diagram                         |

|     | 17.3.1 General Purpose I/O                 |

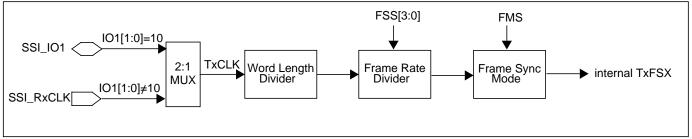

|     | 17.3.2 Frame Synchronization               |

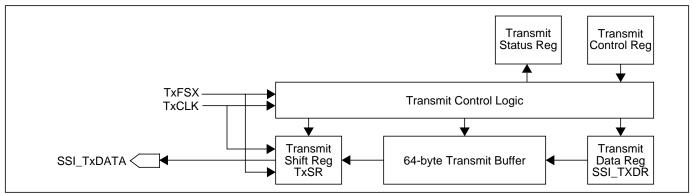

|     | 17.3.3 SSI Transmit                        |

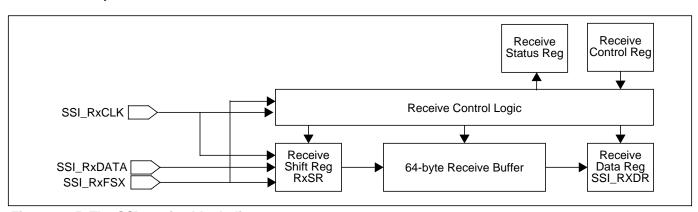

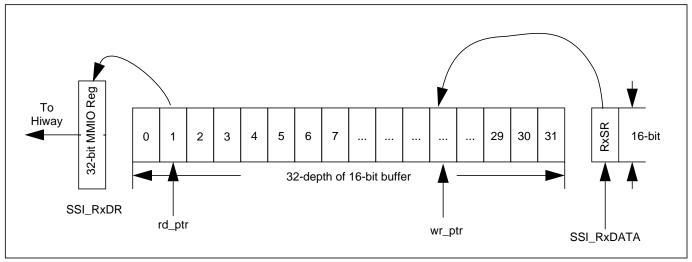

|     | 17.3.4 SSI Receive                         |

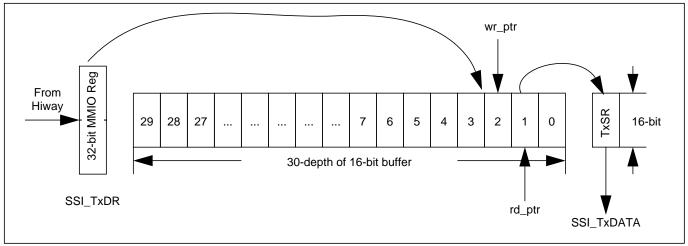

|     | 17.4 SSI Transmit operation                |

|     | 17.4.1 Setup SSI_CTL                       |

|     | 17.4.2 Operation Details                   |

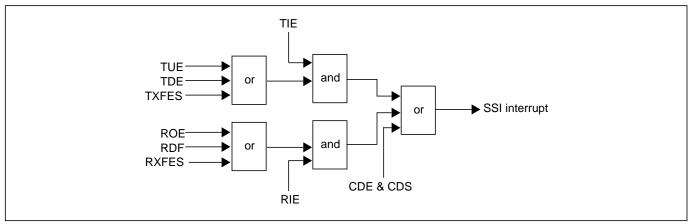

|    | 17.4.3 Interrupt and Status                          | -5  |

|----|------------------------------------------------------|-----|

|    | 17.5 SSI Receive Operation                           | -6  |

|    | 17.5.1 Setup SSI_CTL                                 | -6  |

|    | 17.5.2 Operation Details                             | -6  |

|    | 17.5.3 Interrupt and Status                          | -6  |

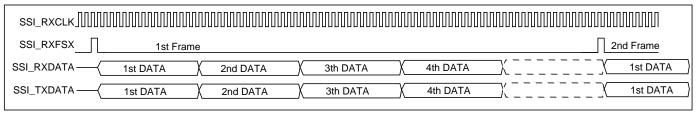

|    | 17.6 Frame Timing                                    | -6  |

|    | 17.7 Interrupt Generation                            | -7  |

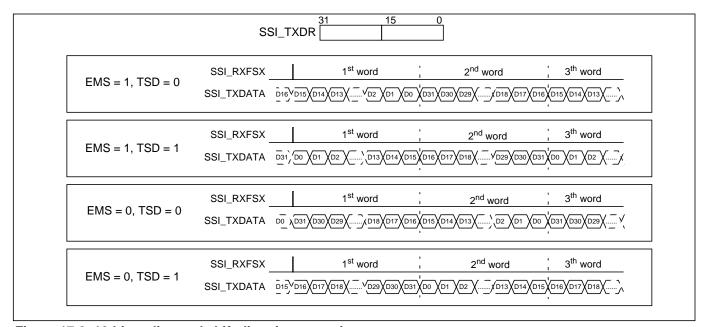

|    | 17.8 16-bit Endian-ness and Shift Direction          | -7  |

|    | 17.9 SSI Test Modes                                  | -8  |

|    | 17.9.1 Remote Loopback                               | -8  |

|    | 17.9.2 Local Loopback                                | -8  |

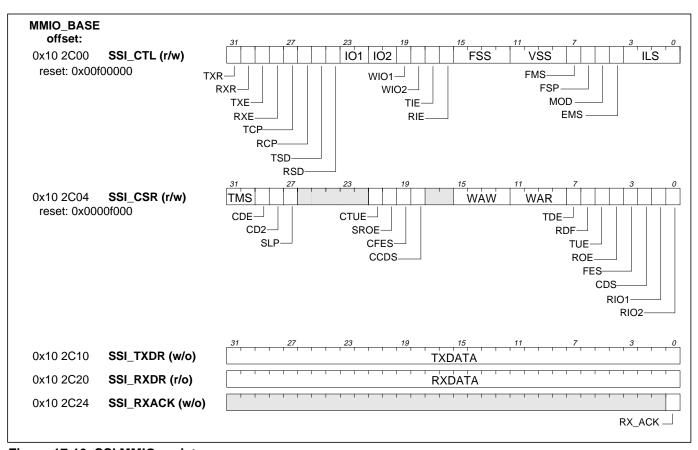

|    | 17.10 MMIO Registers                                 | -8  |

|    | 17.10.1 SSI Control Register (SSI_CTL)               |     |

|    | 17.10.2 SSI Control/Status Register (SSI_CSR)        | -11 |

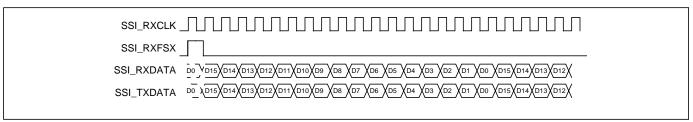

|    | 17.11 Timing Diagrams                                |     |

|    | 17.12 Power Down                                     | -12 |

| 18 | JTAG Functional Specification                        |     |

|    | 18.1 Overview                                        | -1  |

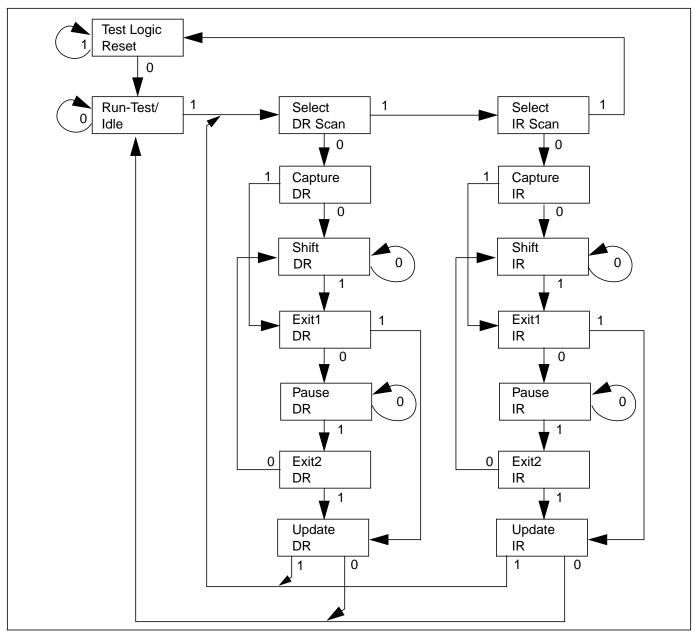

|    | 18.2 Test Access Port (TAP)                          |     |

|    | 18.2.1 TAP Controller                                | -1  |

|    | 18.2.2 TM1300 JTAG Instruction Set                   | -2  |

|    | 18.3 Using JTAG for TM1300 Debug                     | -3  |

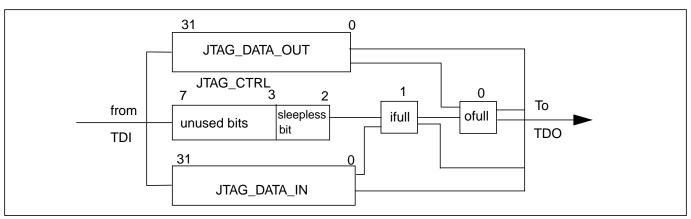

|    | 18.3.1 JTAG Instruction and Data Registers           | -4  |

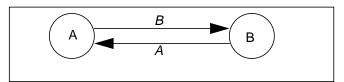

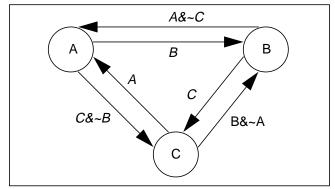

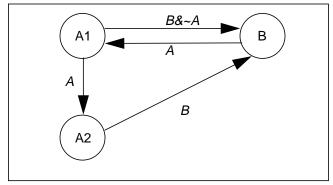

|    | 18.3.2 JTAG Communication Protocol                   | -5  |

|    | 18.3.3 Example Data Transfer Via JTAG                | -5  |

|    | 18.3.3.1 Transferring data to TriMedia via JTAG      | -5  |

|    | 18.3.3.2 Transferring data from TriMedia via JTAG    | -6  |

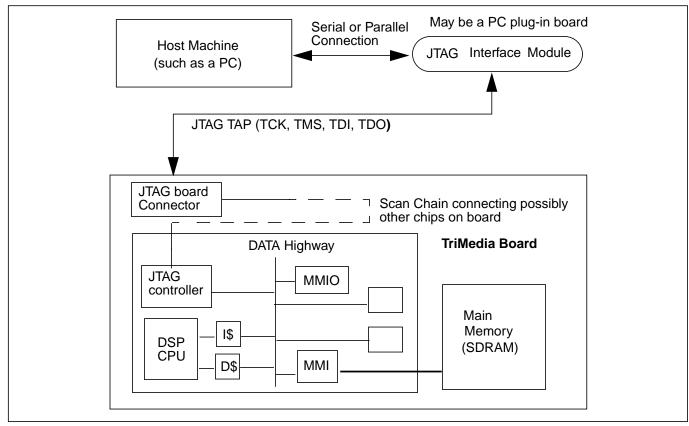

|    | 18.3.4 JTAG Interface Module                         | -6  |

| 19 | On-Chip Semaphore Assist Device                      |     |

|    | 19.1 SEM Device Specification                        | -1  |

|    | 19.2 Constructing a 12-Bit ID                        | -1  |

|    | 19.3 Which SEM to Use                                | -1  |

|    | 19.4 Usage Notes                                     | -1  |

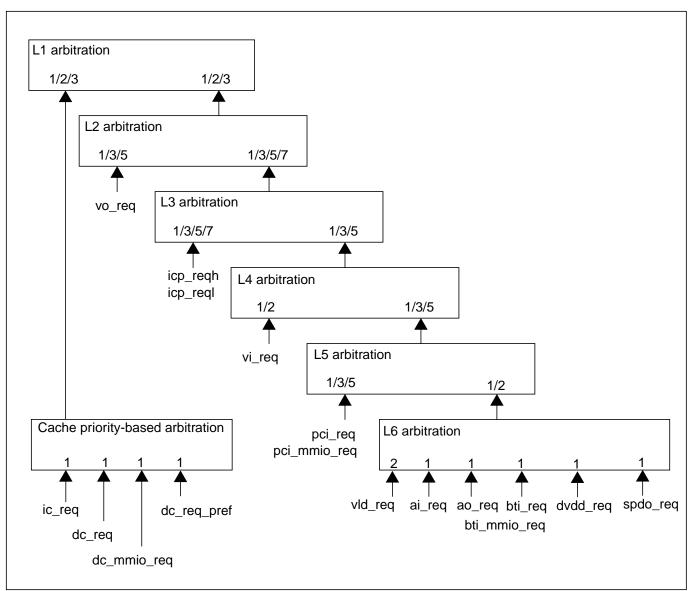

| 20 | Arbiter                                              |     |

|    | 20.1 Arbiter Features                                | -1  |

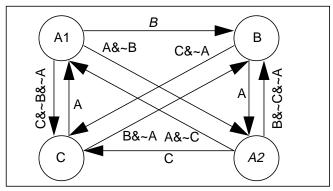

|    | 20.2 Dual Priorities with Priority Raising Mechanism | -1  |

|    | 20.3 Round Robin Arbitration                         | -2  |

|    | 20.3.1 Weighted Round Robin Arbitration              | -2  |

|    |                                                      |     |

|    | 20.3.2 Arbitration Levels                              | 20-3  |

|----|--------------------------------------------------------|-------|

|    | 20.4 Arbiter Architecture                              | 20-4  |

|    | 20.5 Arbiter programming                               | 20-5  |

|    | 20.5.1 Latency Analysis                                | 20-5  |

|    | 20.5.2 Bandwidth Analysis                              | 20-6  |

|    | 20.6 Extended Behavior Analysis                        | 20-7  |

|    | 20.6.1 Extended Bandwidth Analysis                     | 20-7  |

|    | 20.6.2 Extended Latency Analysis                       | 20-7  |

|    | 20.6.3 Raising Priority                                | 20-8  |

|    | 20.6.4 Conclusion                                      | 20-8  |

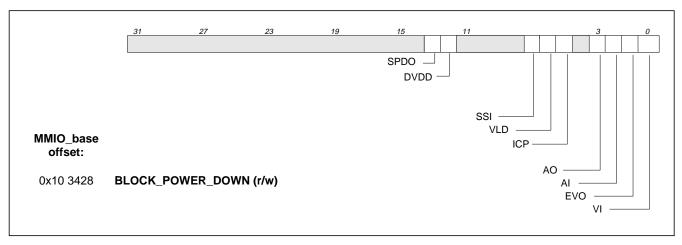

| 21 | Power Management                                       |       |

|    | 21.1 Overview                                          | 21-1  |

|    | 21.2 Entering and Exiting Global Power Down Mode       |       |

|    | 21.3 Effect Of Global Power Down On Peripherals        |       |

|    | 21.4 Detailed Sequence of Events For Global Power Down |       |

|    | 21.5 MMIO Register POWER_DOWN                          |       |

|    | 21.6 Block Power Down                                  |       |

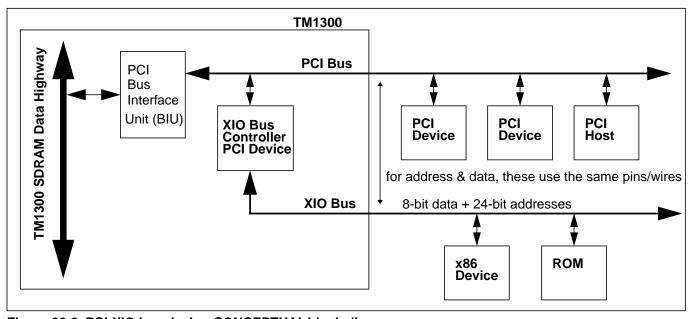

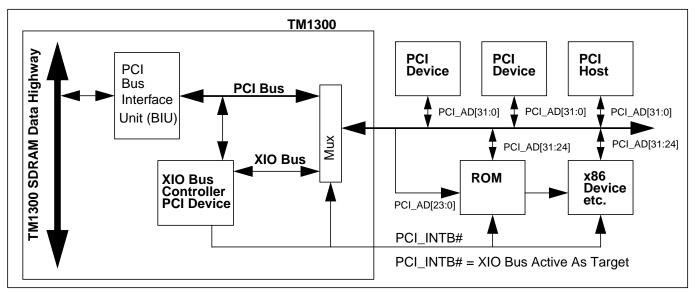

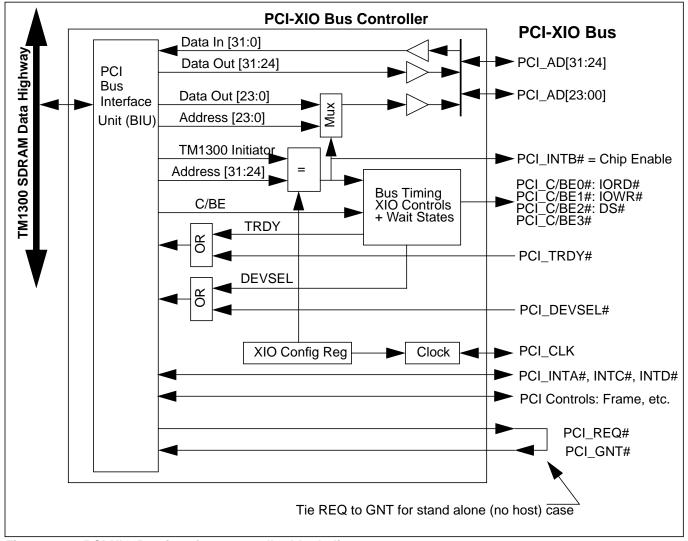

| 22 | PCI-XIO External I/O Bus                               |       |

|    | 22.1 Summary Functionality                             | 22-1  |

|    | 22.1.1 Description                                     |       |

|    | 22.2 Block Diagram                                     |       |

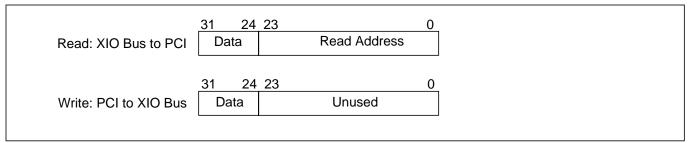

|    | 22.3 Data Formats                                      |       |

|    | 22.4 Interface                                         |       |

|    | 22.4.1 PCI-XIO Bus Interface Design                    | 22-5  |

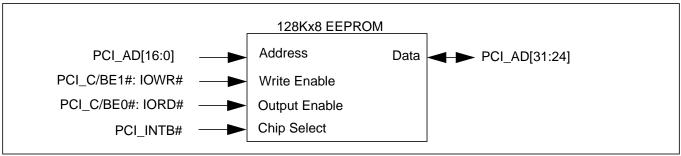

|    | 22.4.1.1 Flash EEPROM                                  |       |

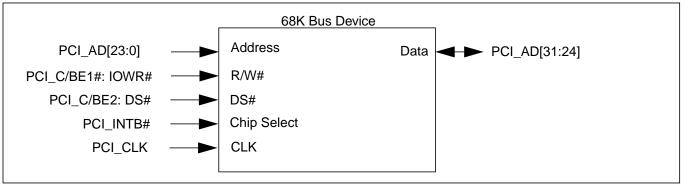

|    | 22.4.1.2 68K Bus I/O device                            | 22-6  |

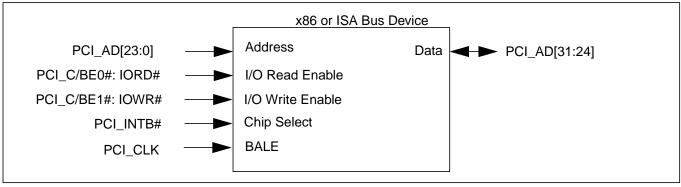

|    | 22.4.1.3 x86/ISA Bus I/O device                        | 22-6  |

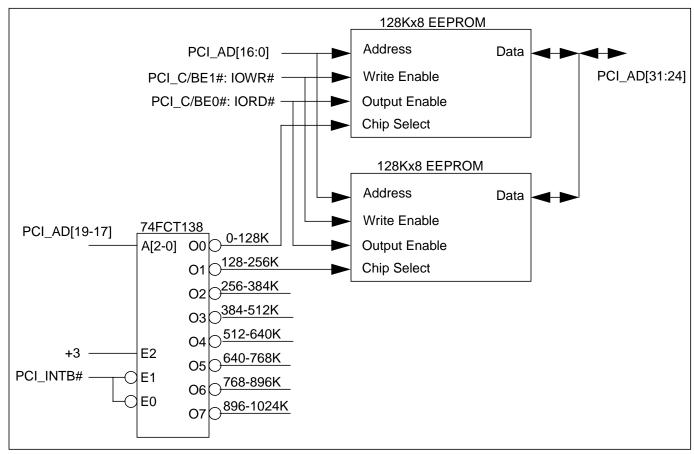

|    | 22.4.1.4 Multiple Flash EEPROM                         | 22-6  |

|    | 22.5 XIO_CTL MMIO Register                             | 22-7  |

|    | 22.5.1 PCI_CLK Bus Clock Frequency                     | 22-7  |

|    | 22.5.2 Wait State Generator                            | 22-8  |

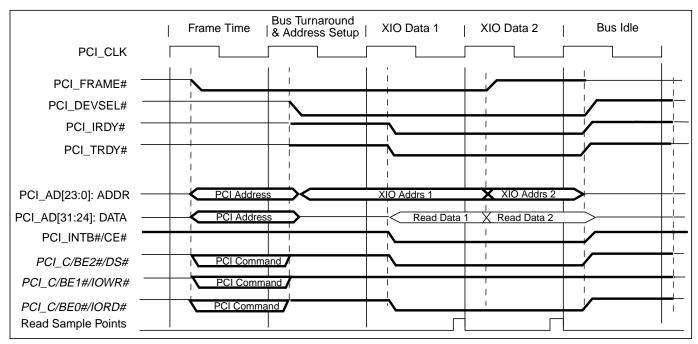

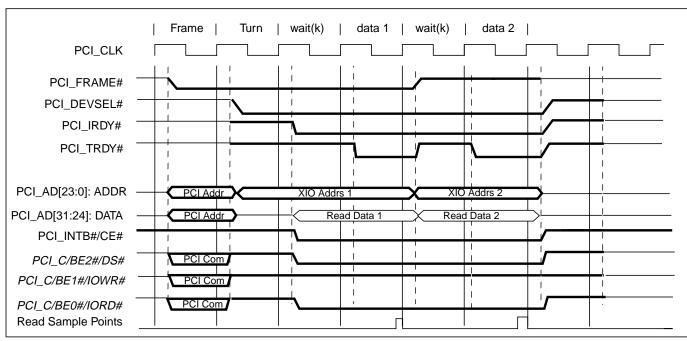

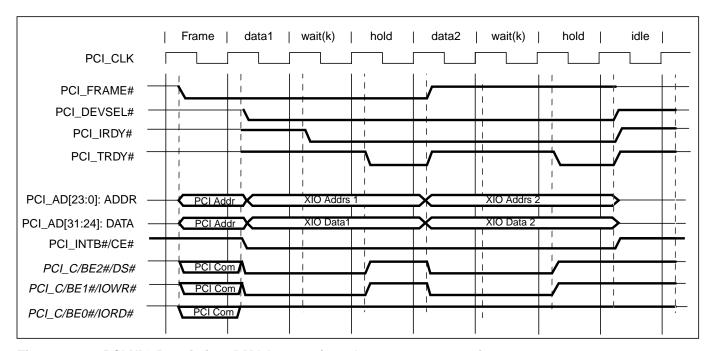

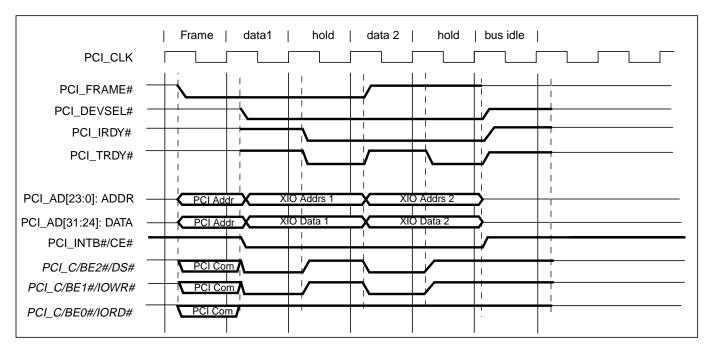

|    | 22.6 PCI-XIO Bus Timing                                | 22-8  |

|    | 22.7 PCI-XIO Bus Controller Operation and Programming  | 22-12 |

| Α  | DSPCPU Operations for TM1300                           |       |

|    | A.1 Alphabetic Operation List                          | A-1   |

|    | A.2 Operation List By Function                         |       |

|    | alloc                                                  | A-3   |

|    | allocd                                                 |       |

| allocr A-5         |

|--------------------|

| allocx             |

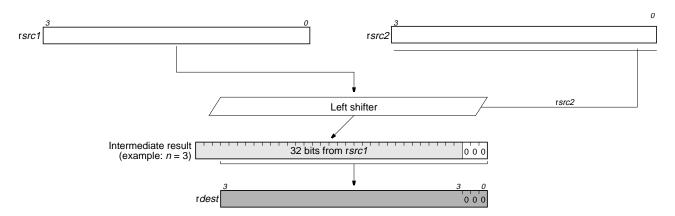

| asl A-7            |

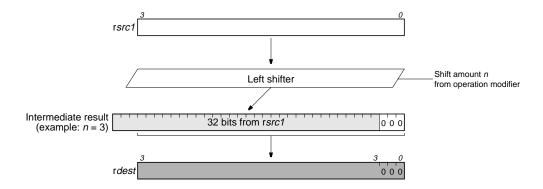

| asli               |

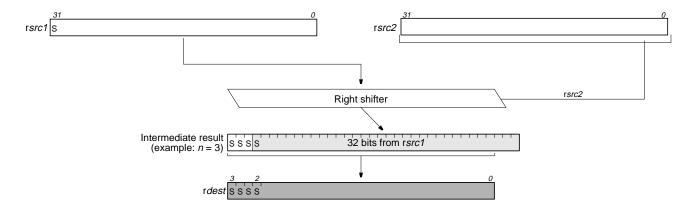

| asr A-9            |

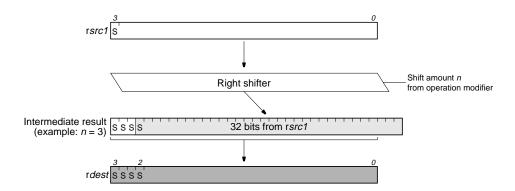

| asri A-10          |

| bitand A-11        |

| bitandinv A-12     |

| bitinv A-13        |

| bitor              |

| bitxor             |

| borrow             |

| carry A-17         |

| curcycles          |

| cycles A-19        |

| dcb                |

| dinvalid A-21      |

| dspiabs            |

| dspiadd            |

| dspidualabs        |

| dspidualadd        |

| dspidualmul        |

| dspidualsub        |

| dspimul            |

| dspisub A-29       |